Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

# CLOSED LOOP CONTROL OF BIDIRECTIONAL BUCK-BOOST CONVERTER IN A SMART GRID USING PHOTOVOLTAIC AND ENERGY STORAGE SYSTEMS

<sup>1</sup>Mr. K. Vijaya Kumar,<sup>2</sup>Mrs. B. Sindhuja,<sup>3</sup>Rudru Vijayalakshmi,<sup>4</sup>Pullagura Tharani <sup>1,3</sup>Assistant Professor,<sup>2</sup>Professor,<sup>4</sup>Student

Department Of EEE

Gouthami Institute Of Technology & Management For Women, Proddatur, Ysr Kadapa, A.P

**ABSTRACT**—This paper proposes a new Closed loop control bidirectional buck-boost converter, which is a key component in a photovoltaic and energy storage system (PV-ESS). Conventional bidirectional buck-boost converters for ESSs operate in discontinuous conduction mode (DCM) to achieve zero-voltage-switching turn-on for switches. However, operation in DCM causes high ripples in the output voltage and current, as well as low power-conversion efficiency. To improve on the performance of the conventional converter, the proposed converter has a new combined structure of a cascaded buck-boost converter and an auxiliary capacitor. The combined structure of the proposed converter reduces the output current ripple by providing a current path and the efficiency is increased. The proposed Closed loop control converter has a maximum efficiency of 98%, less than 5.14 Vp.p of output voltage ripple, and less than 7.12 Ap.p of output current ripple. These results were obtained at an input voltage of 160 V, switching frequency of 45 kHz, output voltage of 80 ~ 320 V, and output power of 16 ~ 160 W. The experimental results show that the proposed converter has improved performance compared to the conventional converter.

Index Terms—DC-DC power conversion, Energy storage, Pulse width modulated power converters

#### **I.INTRODUCTION**

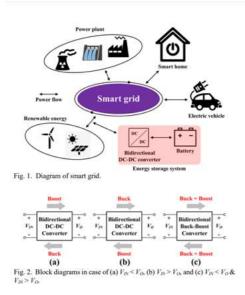

SMART grid (Fig. 1) is future electric energy system that has been studied to reduce mismatching between sources of electricity (such as renewable energy and power plants) and electricity consumers (homes, vehicles, factories, etc.). However, the energy production of renewable energy depends on environmental conditions. Therefore, an energy storage system (ESS) is needed in a smart grid to provide stability and efficiently manage the renewable energy [1-3]. An ESS consists of a battery that stores electric energy and a bidirectional

DC-DC converter that transfers energy from the battery and renewable energy source in both directions [4-9].

#### ISSN PRINT 2319 1775 Online 2320 7876

Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

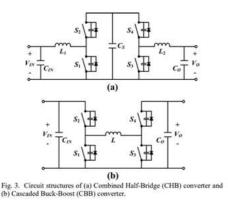

A conventional bidirectional DC-DC converter uses a half-bridge converter with two switches based on a buck or boost DC-DC converter. In the buck mode of the converter, electric energy is transferred from a high voltage (HV) port to the low voltage (LV) port. In boost mode, the electric energy is transferred from the LV port to the HV conventional bidirectional The port. converter has a limitation in that it can only be operated in buck mode in one direction and boost mode in the other direction (Fig. 2(a) and Fig. 2(b) [10-12]. Therefore, when the input is a photovoltaic (PV) module and the output is battery cells in a smart grid, a half bridge converter based on a buck or boost converter cannot be used because of the following reasons: 1) The battery cells repeatedly perform charging and discharging resulting in large operations, voltage variation [13, 14]. 2) The PV module has a large voltage variation that depends on the module temperature and the solar irradiance [15-17]. Thus, the ranges of the input voltage and output voltage can overlap [18, 19].

Bidirectional buck-boost converters (Fig. 2(c)) were introduced for use in cases of overlapping input and output voltages [19-28]. They can operate in both buck and boost modes in both directions. A combined half-bridge (CHB) converter (Fig. 3(a)) is the most basic bidirectional buck-boost converter and has a symmetric structure with respect to the storage capacitor CS [20, 21]. There is one inductor at the input port and one at the output port, which results in low voltage ripples in the input and output. However, because the CHB converter uses two inductors of the same size, it is large and has a low power-conversion efficiency ne due to the DC-offset current of each Cascaded buck-boost (CBB) inductor. converter (Fig. 3(b)), along with the CHB converter, has been commonly used in ESSs. Compared with the CHB converter, CBB converter is smaller and has higher ne because it uses only one inductor L [19, 22-28]. Recently, research has been actively conducted on bidirectional buck-boost DC-DC converters in discontinuous conduction mode (DCM) because this mode can achieve zero-voltage-switching (ZVS) turn-on of the switches [19, 26-28]. However, operation in DCM increases the current ripple of L, which affects the output current ripple and

#### Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

increases the output voltage ripple. In this paper, an enhanced CBB converter is proposed to improve on the performance of the conventional CBB converter. The proposed converter is targeted to a PV-ESS system that uses a micro-inverter, which has been widely used in a smart grid [29, 30]. The converter has a new combined structure of a CBB converter and an auxiliary capacitor. This structure can reduce the output voltage ripple and increase  $\eta$ e by effectively reducing the output current ripple.

# **II.DC-DC CONVERTERS**

A DC-DC converter with a high step-up voltage, which can be used in various applications like automobile headlights, fuel cell energy conversion systems, solar-cell energy conversion systems and battery backup systems for uninterruptable power supplies. Theoritically, dc-dc a boost converter can attain a high step-up voltage with a high effective duty ratio.But,in practical, the step-up voltage gain is restricted by the effect of power switches and the equivalent series resistance(ESR) of inductors and capacitors.

Generally a conventional boost converter is used to get a high-step-up voltage gain with a large duty ratio. But, the efficiency and the voltage gain are restricted due to the losses of power switches and diodes, the equivalent series resistance of inductors and capacitors and the reverse recovery problem of diodes. Due to the leakage inductance of the transformer, high voltage stress and power dissipation effected by the active switch of these converters. To reduce the Voltage spike, a resistor-

# III.PROJECT DISCRIPTION AND CONTROL DESIGN PROPOSED DC-DC CONVERTER

# A. Circuit Structure

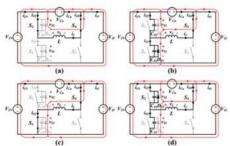

The proposed converter (Fig. 4) consists of a conventional CBB converter and an auxiliary capacitor (Ca), and has а symmetric structure with respect to Ca and L. The CBB converter consists of two capacitors (CIN, CO), four switches (S1, S2, S3, S4), and an inductor (L). Four switches (S1, S2, S3, S4) and an inductor (L) control the direction of energy transfer and the ratio between the input voltage and output voltage. Four switches are turned on in the ZVS condition by operating in DCM. Two capacitors (CIN, CO) reduce the output voltage ripple and noise, and an auxiliary capacitor (Ca) reduces the output current ripple by providing a current path.

#### Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

#### **B.** Principle of Operation

The proposed converter operates with a fixed switching period TS and controls the voltage gain by changing the duty ratio D of the switches (S1, S2, S3, S4) from 0 to 1. Each switch has four states in six operating conditions created by the energy transfer directions between VIN and VO and the types of operation (buck, boost, and buckboost), as shown in Table I. Due to the symmetric structure with respect to Ca and L, the operations are separated by only the types of operation in one direction of energy transfer (VIN  $\rightarrow$  VO).

To simplify the analysis of the operation, the following assumptions are made: 1) the inductor and all capacitors are lossless, 2) the voltage ripples of CIN, Ca, and CO are small enough to assume that VIN, VCa, and VO are constant voltage sources, and 3) the converter operates in steady state.

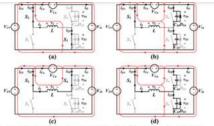

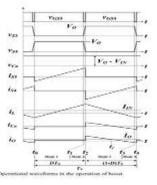

(1) Buck mode When the proposed converter operates in buck mode, it has four distinct operating modes (Mode  $1 \sim 4$ ). The equivalent circuits and operating waveforms are shown in Fig. 5 and Fig. 6.

Mode 1 (Fig. 5(a),  $t0 \le t \le t1$ ) starts when S2 is turned on. At t = t0, S2 achieves ZVS turn-on because the body diode DS2 of S2 is turned on before t = t0. Then, the voltage vL of L becomes VIN – VO, and the current iL of L is expressed as

$$i_{L}(t) = i_{L}(t_{0}) + \frac{V_{IN} - V_{O}}{L}(t - t_{0}). \quad (1)$$

The current  $i_{S2}$  of  $S_{2}$  is equal to  $i_{L}$ , so  $i_{S2}$  is expressed as

$$i_{S2}(t) = i_{L}(t_{0}) + \frac{V_{IN} - V_{O}}{L}(t - t_{0}).$$

In this mode, the current iCa of Ca, the current iCo of CO, the output current iO, and the load current IO have the following relations: iO = iCo + IO,  $iCo = iCa \cdot CO/Ca$ ,

and iO = iL - iCa. Therefore, iCa and iO can be derived as

$$i_{Ca}(t) = \frac{C_a}{C_a + C_O} [i_L(t) - I_O]$$

$$i_O(t) = \frac{C_O}{C_a + C_O} i_L(t) + \frac{C_a}{C_a + C_O} I_O.$$

(2)

The voltage  $v_{Ca}$  across the auxiliary capacitor  $C_a$  is expressed as  $v_{Ca}(t) = V_{Ca} + \Delta v_{Ca,dC}(t)$ where  $V_{Ca}$  and  $\Delta v_{Ca,dC}$  represent the DC voltage and the AC ripple voltage across the  $C_a$  respectively. Because  $V_{Ca} > \Delta v_{Ca,dC}$ ,  $v_{Ca}$  can be approximated as  $v_{Ca}(t) \approx V_{Ca} = V_D - V_{IN}$ .

Mode 2 (Fig. 5(b),  $t1 \le t \le t2$ ) starts when S2 is turned off. At this time, S1 remains in the off state to prevent a shoot-through problem with S1 and S2. In this mode, the output capacitor CS1 of S1 discharges from VIN to 0, and the output capacitor CS2 of S2 charges from 0 to VIN. Shortly after the discharging of CS1 and charging of CS2 are finished, the body diode DS1 of S1 is turned on. Mode 3 (Fig. 5(c),  $t2 \le t \le t3$ ) starts with the ZVS turn-on of S1 because DS1 is turned on before t = t2. Then, vL becomes -VO, and thereby iL is expressed as

$$i_L(t) = i_L(t_2) - \frac{V_O}{L}(t - t_2).$$

(3)

Because iO = iL - iCa, iO = iCo + IO, and  $iCo = iCa \cdot CO/Ca$ , iCa and iO are expressed as

The current iS1 of S1 is equal to -iL, so iS1 is obtained as

$$i_{S1}(t) = -i_L(t_2) + \frac{V_O}{L}(t-t_2).$$

Because iO = iL - iCa, iO = iCo + IO, and  $iCo = iCa \cdot CO/Ca$ , iCa and iO are expressed as

$$i_{Ca}(t) = \frac{C_a}{C_a + C_O} [i_L(t) - I_O]$$

$$\tag{4}$$

$$i_{O}(t) = \frac{C_{O}}{C_{a} + C_{O}} i_{L}(t) + \frac{C_{a}}{C_{a} + C_{O}} I_{O}.$$

(5)

Mode 4 (Fig. 5(d),  $t3 \le t \le t4$ ) starts when S1 is turned off and S2 remains in the off

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

state. In this mode, CS1 charges from 0 to VIN, and CS2 discharges from VIN to 0. Shortly after the charging of CS1 and discharging of CS2 are finished, DS2 is turned on. At t = t0, iL has an initial value of iL(t0), and iL(t0) is obtained as follows: By inserting t = t2 into (1), the current ripple  $\Delta$ iL of iL is obtained as

$$\Delta i_{L} = i_{L}(t_{2}) - i_{L}(t_{0}) = \frac{V_{IN} - V_{O}}{L} DT_{S}, \qquad (6)$$

where DTS = t2 - t0. The average current of L for one TS is obtained as = IO by applying the ampere-second balance law for capacitors to L () () () Ca Co ++= Itititi O . Then, iL(t0) = -  $\Delta iL/2$  is represented as

Fig. 5. Circuit diagrams for the operation of buck; (a) Mode 1, (b) Mode 2, (c) Mode 3, and (d) Mode 4.

(2) Boost mode

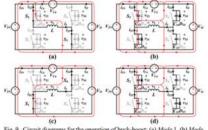

The boost operation also has four distinct operating modes (Mode 1 ~ 4), and the equivalent circuits and operating waveforms are shown in Fig. 7 and Fig. 8, respectively. Mode 1 (Fig. 7(a),  $t0 \le t \le t1$ ) starts when S3 is turned on. At t = t0, S3 achieves ZVS turn-on because the body diode DS3 of S3 is turned on before t = t0. Then, vL becomes VIN, and iL is expressed as  $i_{L}(t) = i_{L}(t_{0}) + \frac{V_{IN}}{L}(t-t_{0}).$ (9)

The current iS3 of S3 is the same as iL, so iS3 is expressed as

$$i_{S3}(t) = i_L(t_0) + \frac{V_{IN}}{L}(t-t_0).$$

Because iO = -iCa, iO = iCo + IO, and  $iCo = iCa \cdot CO/Ca$ , iCa and iO are expressed as

$$i_{Ca}(t) = -\frac{C_a}{C_a + C_O} I_O$$

$$i_O(t) = \frac{C_a}{C_a + C_O} I_O.$$

(10)

The voltage vCa across the auxiliary capacitor Ca is expressed as  $v_{\alpha}(t) = V_{\alpha} + \Delta v_{\alpha} \cdot c(t)$

$$C_a(t) = V_{Ca} + \Delta V_{Ca,AC}(t).$$

Because Ca Ca AC  $>> \Delta vV$ , , this expression can be approximated as

$v_{Ca}(t) \approx V_{Ca} = V_O - V_{IN}$

Mode 2 (Fig. 7(b),  $t1 \le t \le t2$ ) starts when S3 is turned off and S4 remains in the off state. In this mode, the output capacitor CS3 of S3 charges from 0 to VO, and the output capacitor CS4 of S4 discharges from VO to 0. Shortly after the charging of CS3 and discharging of CS4 are finished, the body diode DS4 of S4 is turned on. Mode 3 (Fig. 7(c),  $t2 \le t \le t3$ ) starts with the ZVS turn-on of S4 because DS4 is turned on before t = t2. Then, vL becomes VIN - VO, and iL is expressed as

$$i_L(t) = i_L(t_2) + \frac{V_{IN} - V_O}{L}(t - t_2).$$

(11)

2896

#### ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

The current iS4 of S4 is equal to -iL, so iS4 is obtained as

$$i_{S4}(t) = -i_L(t_2) - \frac{V_{IN} - V_O}{L}(t - t_2).$$

Because iO = iL - iCa, iO = iCo + IO, and  $iCo = iCa \cdot CO/Ca$ , iCa and iO are expressed as

$$i_{Ca}(t) = \frac{C_a}{C_a + C_O} [i_L(t) - I_O]$$

(12)

$$i_O(t) = \frac{C_O}{C_a + C_O} i_L(t) + \frac{C_a}{C_a + C_O} I_O.$$

(13)

Mode 4 (Fig. 7(d),  $t3 \le t \le t4$ ) starts when S4 is turned off and S3 remains in off-state. In this mode, CS3 discharges from VO to 0 and CS4 charges from 0 to VO. Shortly after the discharging of CS3 and charging of CS4 are finished, DS3 is turned on. By inserting t = t2 into (9),  $\Delta iL$  for boost operation is obtained as

$$\Delta i_{L} = i_{L}(t_{2}) - i_{L}(t_{0}) = \frac{v_{IN}}{L} DT_{S}, \qquad (14)$$

where  $DT_S = t_2 - t_0$ . Because  $\langle i_L \rangle = I_{IN}$  and  $i_L(t_0) = \langle i_L \rangle - \Delta i_L/2$ ,  $i_L(t_0)$  is expressed as

$$i_L(t_0) = I_{IN} - \frac{V_{IN}}{2L} DT_S$$

(15)

$i_L(t_2) = \langle i_L \rangle + \Delta i_L/2$  is expressed as

$$i_L(t_2) = I_{IN} + \frac{V_{IN}}{2L}DT_S.$$

(16)

Fig. 7. Circuit diagrams for the operation of boost; (a) Mode 1, (b) Mode 2, (c) Mode 3, and (d) Mode 4.

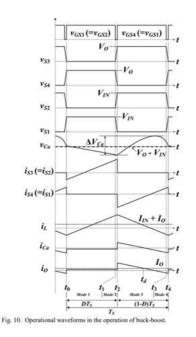

waveforms are shown in Fig. 9 and Fig. 10, respectively. Mode 1 (Fig. 9(a),  $t0 \le t \le t1$ ) starts when S2 and S3 are turned on. At t = t0, S2 and S3 achieve ZVS turn-on because DS2 and DS3 are turned on before t = t0. Then, vL becomes VIN, and iL is expressed as

$$i_{L}(t) = i_{L}(t_{0}) + \frac{V_{IN}}{L}(t - t_{0}).$$

(17)

Both iS2 and iS3 are same as iL, so they are expressed as

$$i_{S2}(t) = i_{S3}(t) = i_L(t_0) + \frac{V_{IN}}{L}(t-t_0).$$

Because iO = -iCa, iO = iCo + IO, and  $iCo = iCa \cdot CO/Ca$ , iCa and iO are expressed as

Fig. 9. Circuit diagrams for the operation of buck-boost; (a) Mode 1, (b) Mode 2, (c) Mode 3, and (d) Mode 4.

$$(t) = -\frac{C_a}{C_a + C_O} I_O$$

$$(18)$$

$$(t) = \frac{C_a}{C_a + C_O} I_O.$$

$$(19)$$

$i_O(t) = \frac{C_a}{C_a + C_O} I_O.$  $v_{Ca}(t)$  is obtained using the equation (18) as

ic.

$$\begin{aligned} v_{Ca}(t) &= v_{Ca}(t_0) + \frac{1}{C_a} \int_{t_0}^t i_{Ca}(t) dt \approx v_{Ca} + \frac{1}{C_a} \left[ \frac{-C_a I_O}{C_a + C_O} (t - t_0) \right] \\ &= V_O - V_{IN} - \frac{I_O}{C_a + C_O} (t - t_0). \end{aligned}$$

Mode 2 (Fig. 9(b),  $t1 \le t \le t2$ ) starts when S2 and S3 are turned off and S1 and S4

#### Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

remain in the off state. In this mode, CS2 and CS3 charge from 0 to VIN and from 0 to VO, respectively. CS1 and CS4 discharge from VIN to 0 and from VO to 0, respectively. Shortly after the charging and discharging processes are finished, the DS1 and DS4 are turned on. Mode 3 (Fig. 9(c),  $t2 \le t \le t3$ ) starts with the ZVS turn-on of S1 and S4 because DS1 and DS4 are turned on before t = t2. Then, vL becomes -VO, and iL is expressed as

$$i_{L}(t) = i_{L}(t_{2}) - \frac{V_{O}}{L}(t - t_{2}).$$

<sup>(20)</sup>

iS1 and iS4 are equal to -iL, so they are obtained as

$$i_{S1}(t) = i_{S4}(t) = -i_L(t_2) + \frac{V_O}{L}(t-t_2).$$

Because iO = iL - iCa, iO = iCo + IO, and  $iCo = iCa \cdot CO/Ca$ , iCa and iO are expressed as

$$i_{Ca}(t) = \frac{C_a}{C_a + C_O} [i_L(t) - I_O]$$

(21)

$$i_O(t) = \frac{C_O}{C_a + C_O} i_L(t) + \frac{C_a}{C_a + C_O} I_O.$$

(22)

vCa is obtained using equations (20) and (21) as

$$\begin{split} v_{Ca}(t) &= \frac{1}{C_a} \int_{t_2}^{t} i_{Ca}(t) dt + v_{Ca}(t_2) \\ &= \frac{1}{C_a + C_O} \bigg[ (i_L(t_2) - I_O) (t - t_2) - \frac{V_O}{2L} (t - t_2)^2 \bigg] + v_{Ca}(t_2). \end{split}$$

Mode 4 (Fig. 9(d),  $t3 \le t \le t4$ ) starts when S1 and S4 are turned off and S2 and S3 remain in the off state. In this mode, CS2 and CS3 discharge from VIN to 0 and from VO to 0, respectively. CS1

and CS4 charge from 0 to VIN and from 0 to VO, respectively. Shortly after the discharging and charging processes are finished, DS2 and DS3 are turned on. By inserting t = t2 into (17),  $\Delta$ iL is obtained for buck-boost operation as

$$\Delta i_{L} = i_{L}(t_{2}) - i_{L}(t_{0}) = \frac{V_{IN}}{L} DT_{S}, \qquad (23)$$

where DTS =  $t^2 - t^0$ . Because = IIN + IO and iL( $t^0$ ) = - $\Delta iL/2$ , iL( $t^0$ ) is expressed as

$$i_L(t_0) = I_{IN} + I_O - \frac{V_{IN}}{2L} DT_S, \qquad (24)$$

and  $iL(t2) = +\Delta iL/2$  is expressed as

$$i_{L}(t_{2}) = I_{IN} + I_{O} + \frac{V_{IN}}{2L} DT_{S}.$$

(25)

$$\underbrace{s_{0}}_{t_{1}} \underbrace{s_{0}}_{t_{1}} \underbrace{s_{0}} \underbrace{s_{0}}_{t_{1}} \underbrace{s_{0}} \underbrace{s_{0}} \underbrace$$

where IC,rms is the RMS value of the capacitor current, and RC is the ESR of the

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

capacitor. The voltages and currents of the key power components for calculating these power losses have different values for the different operating modes (Table II). The theoretical efficiency of the proposed converter can be calculated by inserting voltage and current values into the equations  $(43 \sim 49)$  related to the power loss calculations.

#### C. Operation of the Controller

The proposed converter is controlled by pulse width modulation (PWM) signals (vg1 ~ vg4), which are generated by the voltagemode control (Fig. 11(a)). Two voltages (VIN and VO) are sensed to implement the voltage-mode control and protect the over voltage. VO is used as an output voltage for generating the PWM control signal of the main switch in the energy transfer direction from VIN to VO, and VIN is used as an output voltage in the opposite direction. The current of inductor is sensed to protect against over current.

Fig. 11(b) represents a block diagram of the digital controller for the proposed converter. When the energy transfer direction is expressed by the demand of the system, the direction selector determines the sensing output voltage (VIN or VO) needed for the voltage mode control. The voltage-mode PI controller then generates the duty ratio D of the main switch by comparing the sensed voltage with the reference voltage. The mode selector informs the PWM modulator of the operating mode of the proposed converter determined by the sensed VIN and VO. Finally, using the information from the mode selector and voltage mode controller, the PWM modulator and the switch

|                                                |                                                                                                                                                                                                     | OF THE KEY POWER O<br>AIN CAUSES OF POWE                                                                                                                                                                              |                                                                                                                                                                                                                                                                                |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Five main<br>causes of<br>power<br>dissipation | Operating modes                                                                                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                |

|                                                | Buck mode                                                                                                                                                                                           | Boost mode                                                                                                                                                                                                            | Buck-Boost mode                                                                                                                                                                                                                                                                |

| Switching<br>loss of<br>switch                 | $\begin{split} & V_{S3,ann-eff} \\ &= V_{S2,ann-eff} = V_{SS} \\ &I_{S3,ann-eff} \\ &= -I_0 + \frac{V_{IS} - V_0}{2L} DT_S \\ &I_{S2,ann-eff} \\ &= I_0 + \frac{V_{IS} - V_0}{2L} DT_S \end{split}$ | $\begin{split} & V_{S\lambda,hom-off} \\ = V_{S\lambda,hom-off} = V_O \\ & I_{S\lambda,hom-off} \\ = I_{D_X} + \frac{V_{D_X}}{2L} DT_X \\ & I_{S\lambda,hom-off} \\ = -I_{D_X} + \frac{V_{D_X}}{2L} DT_X \end{split}$ | $\begin{split} & F_{S1,ham-off} = F_{S2,ham-off} = F_{IN} \\ & = F_{S2,ham-off} = F_{IN} \\ & = F_{S4,ham-off} = F_{S3,ham-off} \\ & = I_{S1,ham-off} = I_{S3,ham-off} \\ & = I_{IN} + I_0 + \frac{V_{IN}}{2L} DT_S \\ & = -I_{IN} - I_0 - \frac{V_{IN}}{2L} DT_S \end{split}$ |

| Conduction<br>loss of<br>switch                | $\begin{split} I_{S1,com} &= \sqrt{1-D} I_{L,com} \\ I_{S2,com} &= \sqrt{D} I_{L,com} \\ I_{S4,com} &= I_{L,com} \end{split}$                                                                       | $\begin{split} I_{SS,sum} &= \sqrt{D} I_{L,sum} \\ I_{S4,sum} &= \sqrt{1-D} I_{L,sum} \\ I_{S1,sum} &= I_{L,sum} \end{split}$                                                                                         | $I_{SLows} = \sqrt{1 - D}I_{Lows}$ $I_{S2ows} = \sqrt{D}I_{Lows}$ $I_{S3ows} = \sqrt{D}I_{Lows}$ $I_{S4ows} = \sqrt{1 - D}I_{Lows}$                                                                                                                                            |

| Winding<br>loss of<br>inductor                 | $I_{L,rms} = \sqrt{I_O^2 + \frac{V_{LS} - V_O}{12L}DT_S}$                                                                                                                                           | $I_{L,max} = \sqrt{I_{LY}^2 + \frac{V_{LY}}{12L}DT_X}$                                                                                                                                                                | $I_{L,out} = \sqrt{(I_{IN} + I_O)^2 + \frac{V_{IN}}{12L}DT_3}$                                                                                                                                                                                                                 |

| Core loss of<br>inductor                       | $\Delta I_L = \frac{V_{IN} - V_O}{L} DT_S$                                                                                                                                                          | $\Delta i_L = \frac{V_{IN}}{L} DT_S$                                                                                                                                                                                  | $\Delta i_L = \frac{V_{LN}}{L} DT_X$                                                                                                                                                                                                                                           |

| ESR lass of<br>capacitor                       | $I_{Ca,rms} = I_{Ca,rms}$ $= \frac{V_{IN} - V_O}{4\sqrt{M}} DT_N$                                                                                                                                   | $I_{Ca,ram} = I_{Ca,ram}$ $= \frac{1}{2} \sqrt{1 - D} I_{L,ram}$                                                                                                                                                      | $I_{Ca,ram} = I_{Ca,ram}$ $\approx \frac{1}{2}\sqrt{1-D}I_{L,ram}$                                                                                                                                                                                                             |

selector generates four gate signals (vg1  $\sim$  vg4), which control the proposed converter.

#### **IV.SIMULATION RESULTS**

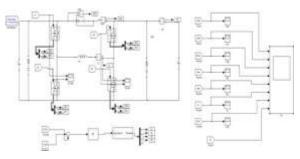

# Fig: Circuit Diagram of BOOST Converter

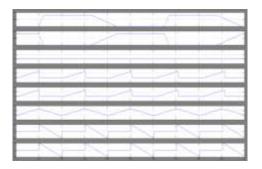

Fig: Simulation Results for BOOST Converter

### ISSN PRINT 2319 1775 Online 2320 7876

Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

Fig: Circuit Diagram of BUCK Converter

# Fig: Simulation Results for BUCK Converter

Fig.: Circuit Diagram of BUCK-BOOST Converter

Fig.: Simulation Results for BUCK-BOOST Converter

# Fig.: Circuit Diagram of CLOSED BUCK Converter

Fig.: Simulation Results for CLOSED BUCK Converter

Fig.: Circuit Diagram of CLOSED BOOST Converter

#### ISSN PRINT 2319 1775 Online 2320 7876

Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

# Fig.: Simulation Results for CLOSED BOOST Converter

#### **V.CONCLUSION**

A new Closed loop control of bidirectional buck-boost converter was proposed in this paper. The proposed converter effectively had lower output current ripple than the conventional CBB converter, which was achieved by providing a bypass path for the output current. The reduced output current ripple enabled lower output voltage ripple and higher powerconversion efficiency compared to the conventional converter. The proposed converter had a maximum efficiency of 98% at VIN = 160 V, VO = 80 ~ 320 V, PO = 16 ~ 160 W, and fS = 45 kHz, and the output voltage ripple was less than 5.14 Vp.p. These results show that the proposed converter is suitable for PV-ESS in a smart grid, which requires a Closed loop control of bidirectional buck-boost converter with high efficiency and low ripples in the output voltage and current.

#### **FUTURE SCOPE:**

The Fuzzy based bidirectional buckboost converter enhances the stability of the system and improves the dynamic response of the system operating in a better way and it has also effectively enhanced the damping of bidirectional buck-boost converter simulation results.

#### REFERENCES

M. Sechilariu, W. Baochao, and F. Locment, "Building integrated photovoltaic system with energy storage and smart grid communication," IEEE Trans. Ind. Electron., vol. 60, no. 4, pp. 1607–1618, Apr. 2013.

[2] B. K. Bose, "Power electronics, smart grid, and renewable energy systems," in Proc. IEEE, vol. 105, no. 11, Nov. 2017.

[3] L. Park, Y. Jang, S. Cho, and J. Kim, "Residential demand response for renewable energy resources in smart grid systems," IEEE Trans. Ind. Informat., vol. 13, no. 6, pp. 3165–3173, Dec. 2017.

[4] C. S. Lim and K. J. Lee, "Nonisolated two-phase bidirectional DC-DC converter with zero-voltage-transition for battery energy storage system," Journal of Electrical Engineering & Technology, vol. 12, no. 6, pp. 2237-2246, Nov. 2017.

[5] M. Glavin, P. Chan, S. Armstrong, and W. Hurley, "A stand-alone photovoltaic supercapacitor battery hybrid energy storage system," in Proc. 13th Power Electron. Motion Control Conf., 2008 (EPE-PEMC 2008), pp. 1688–1695.

[6] J.-J. He, K.-W. Hu, and C.-M. Liaw, "On a Battery/Supercapacitor Powered SRM Drive for EV with Integrated Onboard Charger," in IEEE Industrial Technology Conference, Seville, 2015.

[7] S. H. Moon, S. T. Jou, and K. B. Lee, "Performance improvement of a bidirectional DC-DC converter for battery chargers using an LCLC filter," Journal of

#### Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

Electrical Engineering & Technology, vol. 10, no. 2, pp. 742-755, Mar. 2015.

[8] Y. Du, X. Zhou, S. Bai, S. Lukic, and A. Huang, "Review of nonisolated bidirectional DC–DC converters for plug-in hybrid electric vehicle charge station application at municipal parking decks," in Proc. IEEE Appl. Power Electron. Conf., Feb. 2010, pp. 1145–1151.

[9] S. Vazquez, S. M. Lukic, E. Galvan, L. G. Franquelo, and J. M. Carrasco, "Energy storage system for transport and grid application," IEEE Trans. Ind. Electron., vol. 57, no. 12, pp. 3881–3895, Dec. 2010. [10] M. Ahmadi, M. R. Mohammadi, E. Adib, and H. Farzanehfard, "Family of non-isolated zero current transition bi-directional converters with one auxiliary switch," IET Power Electron., vol. 5, no. 2, pp. 158–165, 2012.

[11] H.-L. Do, "Nonisolated bidirectional zero-voltage-switching DC-DC converter," IEEE Trans. Power Electron., vol. 26, no. 9, pp. 2563–2569, Sep. 2011.

[12] L. S. Yang and T. J. Liang, "Analysis and implementation of a novel bidirectional dc–dc converter," IEEE Trans. Ind. Electron., vol. 59, no. 1, pp. 422–434, Jan. 2012.

[13] O. Tremblay, L. Dessaint, and A. Dekkiche, "A generic battery model for the dynamic simulation of hybrid electric vehicles," in Proc. IEEE Vehicle Power Propuls. Conf., Sep. 2007, pp. 284–289. [14] H. Wang, S. Dusmez, and A. Khaligh, "Design and analysis of a full bridge LLC based PEV charger optimized for wide battery voltage range," IEEE Trans. Veh. Technol., vol. 63, no. 4, pp. 1603–1613, Apr. 2014.

[15] B. Marion, "A method for modeling the current voltage curve of a PV module for outdoor conditions," Prog. Photovoltaic Res. Appl., vol. 10, no. 3, pp. 205–214, May 2002.