Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

## Novel Switched Capacitor Converters with Reduced Components for Step-Up Multilevel Inverter Topology

M. Bhaskar<sup>1</sup>, Y. Rajasekhar<sup>2</sup>, S. Thirumalaiah<sup>3</sup>

<sup>1,2,3</sup>Assistant Professor, Department of EEE, Dr. K. V. Subba Reddy Institute of Technology, Kurnool

#### ABSTRACT

This work presents the first proposed basic cell (BC) of a novel switched capacitor converter (SCC). The proposed SCC's generalized structure is then constructed after that. Compared to previous recently produced SCCs, the developed SCC requires less switches, drivers, diodes, capacitors, and conducting switches in the current flow channels and capacitor charging paths. The next development is a switched capacitor multilevel inverter (SCMLI) that makes use of two generalized SCCs. In addition, a cascaded extension of the suggested SCMLI is implemented and examined for both symmetric and asymmetric DC source arrangements. A thorough examination of the best capacitance option for 13 level SCMLI switching capacitors is provided. A thorough comparative analysis reveals that, in comparison to existing SCMLIs, the suggested SCMLI requires less components. In addition, compared to the other SCMLIs, the suggested structure has the lowest cost function per level per boosting factor. The benefits and efficacy of the suggested structure are validated by presenting extensive experimental findings that take into account the fundamental switching frequency scheme. Index Table of Contents: This study presents the first proposed basic cell (BC) of a novel switched capacitor converter (SCC). The proposed SCC's generalized structure is then constructed after that. Compared to previous recently produced SCCs, the developed SCC requires less switches, drivers, diodes, capacitors, and conducting switches in the current flow channels and capacitor charging paths. The next development is a switched capacitor multilevel inverter (SCMLI) that makes use of two generalized SCCs. In addition, a cascaded extension of the suggested SCMLI is implemented and examined for both symmetric and asymmetric DC source arrangements. A thorough examination of the best capacitance option for 13 level SCMLI switching capacitors is provided. A thorough comparative analysis reveals that, in comparison to existing SCMLIs, the suggested SCMLI requires less components. In addition, compared to the other SCMLIs, the suggested structure has the lowest cost function per level per boosting factor. The benefits and efficacy of the suggested structure are validated by presenting extensive experimental findings that take into account the fundamental switching frequency scheme.

**INDEX TERMS:** voltage balance, reduced devices, switched capacitor, multilayer inverter, and boosting factor

#### 1. INTRODUCTION

Recent years, multilevel inverters (MLIs) have become a viable dc to ac power conversion system for different applications such as renewable energy conversion systems, motor drive applications, UPS systems, FACTs applications, induction heating systems, distributed

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

generation systems etc [1-4]. As compared to classic 2-level inverters, MLIs have numerous advantages such as:

(1) They can handle high power level using medium voltage rated semiconductor devices,

(2) They can produce output voltage waveform with better harmonic spectrum,

(3) They are sustained by lower electromagnetic interfaces (EMIs) and lower dv/dt stresses.

Generally, conventional MLIs are categorized into three types: neutral point clamped (NPC) MLI, flying capacitor (FC) MLI and cascaded H-bridge (CHB) MLI. Conventional MLIs become very popular in different industrial applications for generating a specific output voltage level (up-to 5 levels) [6-7]. However, they require large number of components for producing higher level output voltage waveform. NPC-MLI requires large number of dc link capacitors and clamping diodes, FC-MLI requires large number of flying capacitors and CHB-MLI requires large number of isolated dc power supplies. Further, NPC and FC MLIs suffer from capacitor voltage unbalancing problem. In addition, conventional MLIs do not possess inherent output voltage boosting ability (i.e. self-boosting ability) which is desirable for boosting the low output voltage of renewable sources such as photovoltaic array to desired load or grid voltage level.

In recent years, a significant resIn recent years, a significant research interest among researchers is found in topological development of MLI structures and in solving the capacitor voltage unbalancing problem. A number of reduced device count MLIs have been proposed in recent years [8-9]. However, these structures do not have self-boosting ability. By incorporating front-end dc to dc converters [10] or impedance networks [11-12], large number of topologies have been proposed to add boosting feature to conventional MLIs. However, magnetic elements present in these topologies make power circuit bulky and less efficient. A number of auxiliary circuits[13] or complex control algorithms [14] have been proposed to mitigate the capacitor voltage unbalancing problem. However, these methods enhance size, cost and complexity of the inverter structure.

Switched capacitor MLI (SCMLI) is a special kind of MLIs which can produce a boosted sinusoidal output voltage by using reduced number of power supplies. SCMLI uses capacitors as alternate dc sources. Further, SCMLI does not require any auxiliary circuits or complex control algorithms to balance the capacitor voltages. Mac and Ionovici introduced the concept of SCMLI in the year of 1998 [15].

Each module of the proposed structure can produce 5 output voltage levels. In this structure, all capacitors cannot be connected in series with input source at a time. This limits boosting factor as well as output voltage level generation of the structure. A new boost SCMLI was proposed by Barzegarkhoo et. al. in [23]. The proposed structure can produce higher number of voltage levels as compared to others. However, the capacitors utilized in this structure cannot be charged to full dc link voltage which limits its boosting factor. Further, the structure requires large number of switches, capacitors and dc sources when high output voltage level is intended to produce. A cross-switched MLI using novel SCCs was developed by Roy et. al. in [24]. The proposed structure requires lower switches and TSV as compared to others. However, the structure is not modular in nature and the structure requires significantly large number of switches, capacitors and N<sub>path</sub> for producing high quality output voltage. A 5 level SCMLI and its cascaded extension were proposed by Saeedian et. al. [25]. The structure cannot add all capacitor voltages with the input source which limits its boosting factor as well as output voltage level generation. Further, N<sub>path\_C</sub> is higher than others which degrades capacitor voltage and output voltage profiles. Liu et.al. proposed a 7 level SCMLI and its cascaded structure in [26]. Although the structure sustains lower voltage stresses, the

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

structure cannot add all capacitors with the input source which limits its boosting factor and output voltage level. In cascaded form, the proposed structure requires significantly large number of capacitors without enhancing boosting factor of the structure. Peng et. al. proposed a 7 level SCMLI in [27]. Further, a cascaded structure was developed. The structure provides higher boosting factor as compared to others. However, the structure requires H-bridge circuit and requires significantly large number of switches, power diodes, capacitors and N<sub>path</sub> for producing high quality output voltage waveform.

It is observed that the major drawbacks of SCMLIs are

(1) They require significantly large number of components for producing higher level output voltage waveform,

(2) The lower boosting factor of the structures,

(3) The large number of  $N_{\text{path}}$  and  $N_{\text{path}\_C}$  which degrade the quality of output voltage waveform, and

4) High TSV of the structures. Hence, there has a research scope to develop SCMLI structure which requires lower components,  $N_{path}$  and  $_{Npath_C}$ , provides higher boosting factor and lower TSV. Nevertheless, there has a trade-off between the number of components and TSV of the structure at same boosting factor.

In this paper, a novel SCC structure and its extended form are presented first. The proposed SCC has the advantage of minimum and constant  $N_{path}$  and  $N_{path_C}$  as compared to other SCCs whenever the output voltage level of SCC enhances. Further the SCC requires lower number of components as compared to other SCCs. After that a SCMLI and its cascaded extension are presented. The SCMLI structure requires lower number of components,  $N_{path}$  and  $N_{path_C}$  as compared to the recently developed SCMLIs. Detail operating principle, switched capacitor selection procedure have been presented in depth. Cost function comparison among the topologies have been presented. Finally, extensive experimental results are provided to validate the merits and effectiveness of the proposed structure.

#### 2. BASIC CELL OF PROPOSED SCC

Basic Cell (BC) of the proposed SCC is depicted in Fig. 1(a). It comprises of 4 switches ( $S_1$ ,  $S_2$ ,  $S_{1c}$  and  $S_{2c}$ ), 1 diode (D), 2 capacitors ( $C_1$  and  $C_2$ ) and 1 dc power supply ( $V_{in}$ ). Switches  $S_2$ ,  $S_{1c}$  and  $S_{2c}$  do not have anti-parallel diode whereas switch  $S_1$  has anti-parallel diode. Capacitors  $C_1$  and  $C_2$  can be charged up-to  $V_{in}$  by connecting them in parallel with Vin individually by applying appropriate switching states. With these capacitor voltages, BC can produce 3 positive voltage levels ( $+V_{in}$ ,  $+2V_{in}$  and  $+3_{Vin}$ ) across output terminals A and B. Table I shows state of the switches and capacitors corresponding to different output voltage levels. Where '1' and '0' stand for on and off states of switches respectively. Further, charging state, discharging state and not-connected state of the capacitors are indicated by 'C', 'D' and 'NC' respectively.

Fig. 1(b) shows equivalent circuit and current flow paths when  $S_{2c}$  is on. During this switching state,  $C_2$  is connected in parallel with Vin through D. Hence,  $C_2$  accumulates energy from  $V_{in}$  and is charged near about Vin. Charging current for  $C_2$  is  $iC_2$  as shown in Fig. 1(b). Whereas  $C_1$  remains in NC state.

Further, during this switching state, output voltage of BC (i.e.  $V_{AB}$ ) is equal to  $V_{in}$ .

#

Fig.1. Figure presents (a) BC of proposed SCC; Equivalent circuit and current flow paths of proposed BC when  $v_{AB}$  is (b)  $+V_{in}$ , (c)  $+2V_{in}$  and (d)  $+3V_{in}$

Fig. 1(c) depicts equivalent circuit and current flow paths when  $S_2$  and  $S_{1c}$  are turned on. With this switching state,  $C_1$  is connected in parallel with  $V_{in}$  whereas  $C_2$  is connected in series with Vin. Hence,  $C_1$  accumulates energy from  $V_{in}$  whereas  $C_2$  transfers its stored energy towards the load. During this switching state,  $V_{AB}$  is equal to summation of  $V_{in}$  and voltage across  $C_2$  i.e.  $V_{AB}$  is nearly equal to  $2V_{in}$ . The charging current for  $C_1$  is  $iC_1$  as depicted in Fig. 1(c).

When  $S_1$  is turned on, both  $C_1$  and  $C_2$  are connected in series with  $V_{in}$ . Hence, output voltage of BC is equal to near about  $3V_{in}$ . In this state, both capacitors are in discharging state and transfer their stored energy towards the load as depicted in Fig. 1(d) and Table I.

| V <sub>AB</sub> |    |                       | Capacitors |          |   |         |                       |

|-----------------|----|-----------------------|------------|----------|---|---------|-----------------------|

|                 | Sl | <i>S</i> <sub>2</sub> | Slc        | $S_{2c}$ | D | $C_{l}$ | <i>C</i> <sub>2</sub> |

| $+V_{in}$       | 0  | 0                     | 0          | 1        | 1 | NC      | С                     |

| $+2V_{in}$      | 0  | 1                     | 1          | 0        | 0 | С       | D                     |

| $+3V_{in}$      | 1  | 0                     | 0          | 0        | 0 | D       | D                     |

**Table 1 Switch And Capacitor States For Basic Cell**

From this above discussion, it can be concluded that

(a) The proposed BC has self- boosting ability ; boosting factor i.e. the ratio of peak output of BC and input dc source, is equal to 3,

(b) The capacitors can be connected in series/parallel with input supply using simple switching strategy and at the same time output voltage level can be produced,

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

(c) By turning on only one switch  $(S_1)$ , the highest output voltage level (i.e.  $+3V_{in}$ ) can be produced. (d) Stress voltages for  $S_1$ ,  $S_2$ ,  $S_{1c}$  and  $S_{2c}$  are  $2V_{in}$ ,  $V_{in}$ ,  $V_{in}$  and  $2V_{in}$  respectively. Hence, TSV of the BC is 6Vin. Further, peak inverse voltage (PIV) of the diode D is 2Vin.

#### 3. PULSE-WIDTH MODULATION (PWM)

**Pulse-width** modulation (PWM), or pulse-duration modulation (PDM), is a modulation technique used to encode a message into a pulsing signal. Although this modulation technique can be used to encode information for transmission, its main use is to allow the control of the power supplied to electrical devices, especially to inertial<sup>[definition</sup> needed]</sup> loads such as motors. In addition, PWM is one of the two principal algorithms used in photovoltaic solar battery chargers,<sup>[1]</sup>the other being maximum power point tracking.

The average value of voltage (and current) fed to the load is controlled by turning the switch between supply and load on and off at a fast rate. The longer the switch is on compared to the off periods, the higher the total power supplied to the load.

The PWM switching frequency has to be much higher than what would affect the load (the device that uses the power), which is to say that the resultant waveform perceived by the load must be as smooth as possible. The rate (or frequency) at which the power supply must switch can vary greatly depending on load and application, for example Switching has to be done several times a minute in an electric stove; 120 Hz in a lamp dimmer; between a few kilohertz (kHz), to tens of kHz for a motor drive; and well into the tens or hundreds of kHz in audio amplifiers and computer power supplies.

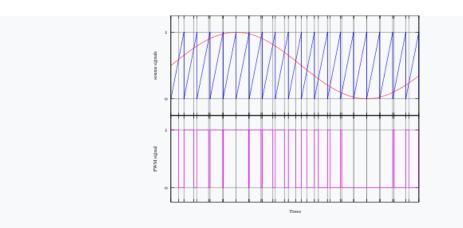

Fig.2: A simple method to generate the PWM pulse train corresponding to a given signal is the intersective PWM: the signal (here the red sine wave) is compared with a sawtooth waveform (blue). When the latter is less than the former, the PWM signal (magenta) is in high state (1). Otherwise it is in the low state (0).

## 4. MULTI LEVEL INVERTER

An inverter is an electrical device that converts direct current (DC) to alternating current (AC) the converted AC can be at any required voltage and frequency with the use of appropriate transformers, switching, and control circuits. Static inverters have no moving parts and are used in a wide range of applications, from small switching power supplies in

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

computers, to large electric utility high voltage direct current applications that transport bulk power. Inverters are commonly used to supply AC power from DC sources such as solar panels or batteries. The electrical inverter is a high power electronic oscillator. It is so named because early mechanical AC to DC converters were made to work in reverse, and thus were "inverted", to convert DC to AC.

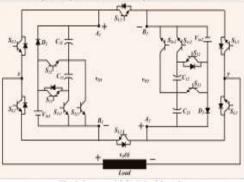

#### **4.1Cascaded H-Bridges inverter**

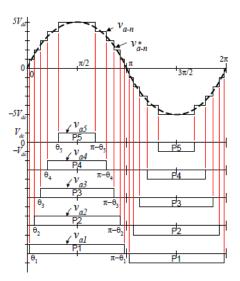

A single phase structure of an m-level cascaded inverter is illustrated in Figure 3. Each separate DC source (SDCS) is connected to a single phase full bridge, or H-bridge, inverter. Each inverter level can generate three different voltage outputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the DC source to the ac output by different combinations of the four switches, S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub>. To obtain  $+V_{dc}$ , switches S<sub>1</sub> and S<sub>4</sub> are turned on, whereas  $-V_{dc}$  can be obtained by turning on switches S<sub>2</sub> and S<sub>3</sub>. By turning on S<sub>1</sub> and S<sub>2</sub> or S<sub>3</sub> and S<sub>4</sub>, the output voltage is 0. The AC outputs of each of the different full bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. The number of output phase voltage levels m in a cascade inverter is defined by m = 2s+1, where s is the number of separate DC sources. An example phase voltage waveform for an 11 level cascaded H-bridge inverter with 5 SDCSs and 5 full bridges is shown in Figure 4. The phase voltage

$$v_{an} = v_{a1} + v_{a2} + v_{a3} + v_{a4} + v_{a5} \qquad \dots (4.1)$$

For a stepped waveform such as the one depicted in Figure 4.2 with s steps, the Fourier Transform for this waveform follows

$V(\omega t) = \frac{4V_{dc}}{\pi} \sum_{n} [\cos(n\theta_1) + \cos(n\theta_2) + \dots + \cos(n\theta_s)] \frac{\sin(n\omega t)}{n}, \text{ where } n = 1,3,5,7\dots$ ...(4.2)

Fig3:Single-phase structure of a multilevel cascaded H-bridges inverter

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

Fig.4. Output phase voltage waveform of an 11 level cascade inverter with 5 separate dc sources.

#### 5. PROJECT DISCRIPTION AND CONTROL DESIGN

#### 5.1 Generalized Structure of Proposed SCC

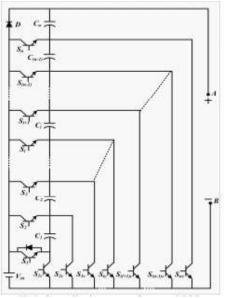

This section presents the development of generalized structure of proposed SCC. The structure is developed by connecting n number of capacitors ( $C_1$  to  $C_n$ ) in series connection as shown in Fig. 2. A switch Sic (i =1 to n) is connected between negative terminal of  $C_i$  (i=1 to n) and negative terminal of  $V_{in}$ . Similarly, a switch  $S_i$  (i=2 to n) is connected between midpoint of 2 capacitors  $C_i$  and  $C_{(i-1)}$  (i=2 to n) and positive terminal of Vin as shown in Fig. 2. Switch  $S_1$  is connected in between positive terminal of  $V_{in}$  and negative terminal of  $C_1$ .

Fig.5. Generalized structure of proposed SCC

Fig.6. Equivalent circuit and current flow paths when (a) C<sub>i</sub> is in charging state and (b) all SCs are in discharging state in generalized SCC

All the capacitors in this structure can be charged to  $V_{in}$  by turning on appropriate switches. For example, i th capacitor,  $C_i$  can be charged to  $V_{in}$  by turning on switches  $S_{i+1}$  and Sic as shown in Fig. 3(a). During this switching state, the generated output voltage appeared across A to B is  $(n-i+1)V_{in}$ . Capacitors connected above of  $C_i$  i.e.  $(C_n$  to  $C_{n-i})$  are in discharging state whereas capacitors connected to lower of  $C_i$  i.e.  $(C_1$  to  $C_{i-1})$  are in NC state. It is observed that the structure needs to conduct only 2 switches to charge any utilized capacitors. Hence,  $N_{path_C}$  for the SCC (i.e.  $N_{path_C_scc}$ ) is 2 and it does not depend on n.

When  $S_1$  is turned on and other switches are in off condition, all the capacitors are connected in series with Vin and highest voltage level of SCC i.e.  $(n+1)V_{in}$  is generated across A to B as shown in Fig. 3(b). During this switching state, all capacitors are in discharging state. As the structure needs to conduct only 1 switch to produce the highest voltage level,  $N_{path}$  for the SCC (i.e.  $N_{path\_scc}$ ) is 1 and it is independent of n.

The number of switches ( $N_{sw\_scc}$ ), drivers ( $N_{dr\_scc}$ ), capacitors ( $N_{cap\_scc}$ ) and TSV (TSV\_SCC) of generalized SCC in terms of n can be expressed by (1)-(3). The structure requires only one power diode (i.e.  $_{Ndio\_scc}=1$ ).

Volume 11 . Iss 12. Dec 2022

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

$$N_{sw_{-}scc} = N_{dr_{-}scc} = 2n \tag{1}$$

(2)

$$N_{cap\_scc} = n \tag{2}$$

$$TSV\_SCC = \frac{1}{4}(5n^2 + 2n + 1) \quad \forall \ n = \text{odd}$$

$$= \frac{1}{4}(5n^2 + 2n) \quad \forall \ n = \text{even} \tag{3}$$

#### **COMPARISON OF PROPOSED SCC WITH OTHER SCCS**

This section presents the comparison of proposed BC and generalized structure of SCC with the recently developed SCCs presented in [15-17, 20-21, 23, 24].

#### A.Comparison of proposed BC with others

Table II shows the comparison of proposed BC with other SCCs in respect of component requirement, boosting factor (B<sub>scc</sub>) and (TSV+PIV). As per Table II, the proposed BC requires lower number of switches and drivers as compared to the SCCs presented in [15-16, 23-24]. The switch per level ( $N_{sw_scc}/N_{L_scc}$ ) for proposed BC is 1.33 which is lower than the SCCs presented in [15-16, 23-24] as shown in Table II. The SCC presented in [17] requires same number of switches and drivers as that for proposed one. However it requires more number of power diodes. The proposed BC has higher  $B_{scc}$  than SCC presented in [23].  $B_{scc}$ for [23] is 2 whereas that for proposed BC is 3. The is due to inability of the SCC presented in [23] to charge the capacitors up-to the full dc supply voltage.

The SCC presented in [20-21] requires lower number of switches as compared to the proposed BC. As per Table II, N<sub>sw scc</sub>/N<sub>L scc</sub> for [20-21] is 1.25 whereas that for proposed BC is 1.33. However, the SCC presented in [20-21] requires two capacitors of different voltage ratings. The maximum voltage rating of utilized capacitors (V<sub>Cmax rating</sub>) for [20-21] is 2V<sub>in</sub> whereas the proposed BC utilizes two capacitors of equal voltage rating as shown in Table II. Each capacitor voltage rating of proposed BC is Vin. This can reduce the cost of the capacitors of proposed BC as compared to the SCC presented in [20-21].

The major advantage of proposed BC is that it requires lower N<sub>path\_scc</sub> than others. As per Table II, N<sub>path scc</sub> of proposed

| <b>Table II</b> Switch And Capacitor States For Proposed 13 Level Scmli In Positive Half Cycle |

|------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------|

| $\frac{t_{\rm f}}{\tilde{t}_{\rm g}}$ | n switches during the limit quarter<br>stycke                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | G. | G  | C <sub>a</sub> | 6  | on switches during the second quarter<br>speke                                                    | ζ <sub>ιί</sub> | G | fr. | C <sub>2</sub> |   |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----------------|----|---------------------------------------------------------------------------------------------------|-----------------|---|-----|----------------|---|

| ÷                                     | $\{l_{1},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{2},l_{$ | 0  | 1  | 0              | п  | $\hat{s}_{11}\hat{s}_{12}\hat{s}_{12}\hat{s}_{12}\hat{s}_{23}\hat{s}_{13}$                        | 0               | D | 3   | 1              | 1 |

| 4                                     | $i_{11}i_{2}i_{3}i_{3}i_{3}i_{3}i_{4}i_{4}i_{6}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C  | 1  | 3              | D  | $s_0, s_0, s_0, s_0, s_0, s_0$                                                                    | D               | D | C   | 3              | 1 |

| +4                                    | $S_{11}S_{21}S_{12}S_{12}S_{12}S_{13}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | K. | C  | 9              | D  | 4:4:4:4:4:4:                                                                                      | Ð.,             | D | x   | C              | 1 |

| 늰                                     | $s_{13}s_{2}s_{43}s_{2}s_{2}s_{2}s_{3}s_{1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C. | 3  | ĸ              | ç. | \$3.34.32.32.343.343                                                                              | R.              | C | 5   | D              |   |

| 4                                     | $I_{11}J_{22}J_{12}J_{22}J_{33}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N. | ¢  | x              | c  | ร้องรับร้องร้อ                                                                                    | x               | £ | x   | C              |   |

| ÷Ĩ                                    | $S_{11}S_{24}S_{12}S_{12}S_{13}S_{2}S_{12}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ņ. | ¢. | \$             | X  | $i_0, i_2, i_3, i_5, i_3, i_6$                                                                    | ¢.;             | ж | x   | ť.             |   |

| 1                                     | $i_{3}i_{2}i_{3}i_{3}i_{3}i_{3}i_{3}i_{2}i_{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ¢  | ĸ  | 4              | R. | $\tilde{s}_2 \tilde{s}_2 \tilde{s}_2 \tilde{s}_2 \tilde{s}_2 \tilde{s}_2 \tilde{s}_3 \tilde{s}_4$ | 0               | ж | 1   | х              |   |

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

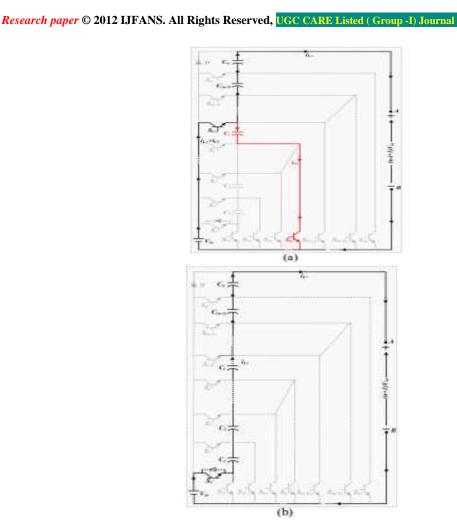

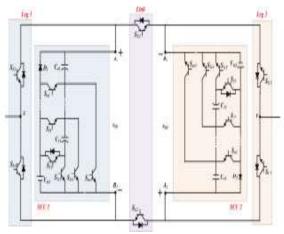

Fig.7. Proposed SCMLI with generalized SCCs

Fig.8. Proposed SCMLI with n=2

Fig.9. Cascaded extension of proposed SCMLI

load by turning on the complementary switches present in Leg 1, Leg 2 and Link circuits. Similarly, for n=2, the proposed structure can produce 31 output voltage levels with asymmetric dc sources ( $V_{in1}=V_{dc}$  and  $V_{in2}=4V_{dc}$ ).

The cascaded extension of proposed SCMLI is shown in Fig. 7. It consists of m number of modules. The required switches  $(N_{sw})$  and drivers  $(N_{dri})$ , capacitors  $(N_{cap})$ , diodes  $(N_{dio})$ , dc sources  $(N_{dc})$ ,  $N_{path}$  and  $N_{path_C}$  can be expressed by (4) and (5).

$$N_{sw} = N_{dr} = (4n + 6)m$$

;  $N_{cap} = 2nm$  (4)

$N_{dc} = N_{dio} = 2m$ ;  $N_{path} = 5m$ ;  $N_{path C} = 2$  (5)

The cascaded SCMLI is analyzed for symmetric and asymmetric dc source configurations. In symmetric configuration, all modules have same magnitude of dc sources as presented by (6).

#### IJFANS INTERNATIONAL JOURNAL OF FOOD AND NUTRITIONAL SCIENCES

## ISSN PRINT 2319 1775 Online 2320 7876

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

The output voltage level and TSV of the structure can be presented by (7) and (8) respectively.

$$V_{inlk} = V_{in2k} = V_{dc} \quad \forall \ k = 1 \text{ to } m \tag{6}$$

$$N_L = 4nm + 4m + 1 \tag{7}$$

$$TSVpu_{symcas} = \frac{5n^2 + 18n + 17}{4(n+1)} \quad \forall \ n = \text{odd} \ ;$$

$$\frac{5n^2 + 18n + 16}{4(n+1)} \quad \forall \ n = \text{even} \tag{8}$$

Further, the proposed cascaded SCMLI is analyzed for asymmetric dc source configuration. In this configuration, magnitude of dc sources, generated output voltage levels and TSV of the proposed structure are presented by (9), (10) and (11) respectively.

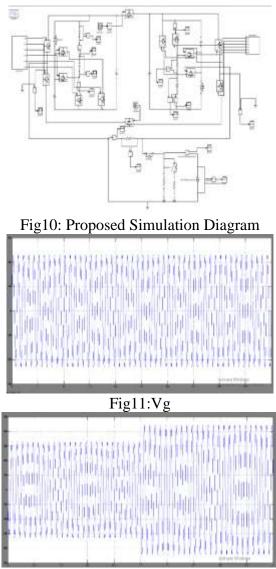

#### 6. SIMULATION RESULTS

Fig12: Ig

Fig: 13 level output voltage and output current

## 7. CONCLUSION

First, a reduced component SCC structure has been proposed in this paper. It has been discussed how the planned SCC's BC operates. Additionally, a generalized SCC has been created. Following that, a two-SCC SCMLI structure is constructed, and the enlarged version of the suggested SCMLI is provided. A thorough examination of the capacitor selection process for the 13 level SCMLI has been provided. When compared to recently produced SCCs and SCMLIs, a detailed comparison study reveals that the suggested SCC and SCMLI structures use less components, Npath and Npath\_C, to produce an output voltage level. Furthermore, out of all the recommended topologies, the proposed SCMLI offers the lowest CF/(NL×B). Comprehensive experimental findings have been provided to confirm the advantages and efficacy of the suggested structures while taking into account the basic switching frequency scheme.

#### 8. REFERENCES

- 1. N. A. Rahim, K. Chaniago and J. Selvaraj, "Single-Phase Seven-Level Grid-Connected Inverter for Photovoltaic System," in IEEE Transactions on Industrial Electronics, vol. 58, no. 6, pp. 2435-2443, June 2011.

- L. QingFeng, W. HuaMin and L. ZhaoXia, "Discuss on the Application of Multilevel Inverter in High Frequency Induction Heating Power Supply," TENCON 2006 - 2006 IEEE Region 10 Conference, Hong Kong, 2006, pp. 1-4.

- 3. Jih-Sheng Lai and Fang Zheng Peng, "Multilevel converters-a new breed of power converters," in IEEE Transactions on Industry Applications, vol. 32, no. 3, pp. 509-517, May-June 1996.

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

- 4. L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo and M. A. M. Prats, "The age of multilevel converters arrives," in IEEE Industrial Electronics Magazine, vol. 2, no. 2, pp. 28-39, June 2008.

- 5. S. Kouro et al., "Recent Advances and Industrial Applications of Multilevel Converters," in IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- 6. J. Rodriguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications," in IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 724-738, Aug. 2002.

- H. Abu-Rub, J. Holtz, J. Rodriguez and G. Baoming, "Medium-Voltage Multilevel Converters—State of the Art, Challenges, and Requirements in Industrial Applications," in IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2581-2596, Aug. 2010.

- 8. K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu and S. Jain, "Multilevel Inverter Topologies With Reduced Device Count: A Review," in IEEE Transactions on Power Electronics, vol. 31, no. 1, pp. 135-151, Jan. 2016.

- 9. R. Samanbakhsh and A. Taheri, "Reduction of Power Electronic Components in Multilevel Converters Using New Switched CapacitorDiode Structure," in IEEE Transactions on Industrial Electronics, vol. 63, no. 11, pp. 7204-7214, Nov. 2016.

- R. Abdullah, N. A. Rahim, S. R. Sheikh Raihan and A. Z. Ahmad, "Five-Level Diode-Clamped Inverter With Three-Level Boost Converter," in IEEE Transactions on Industrial Electronics, vol. 61, no. 10, pp. 5155-5163, Oct. 2014.

- 11. Fang Zheng Peng, "Z-source inverter," in IEEE Transactions on Industry Applications, vol. 39, no. 2, pp. 504-510, March-April 2003.

- 12. P. C. Loh, S. W. Lim, F. Gao and F. Blaabjerg, "Three-Level Z-Source Inverters Using a Single LC Impedance Network," in IEEE Transactions on Power Electronics, vol. 22, no. 2, pp. 706-711, March 2007.

- 13. A. Shukla, A. Ghosh and A. Joshi, "Control of dc capacitor voltages in diode-clamped multilevel inverter using bidirectional buck-boost choppers," in IET Power Electronics, vol. 5, no. 9, pp. 1723-1732, November 2012.

- P. R. Kumar, R. S. Kaarthik, K. Gopakumar, J. I. Leon and L. G. Franquelo, "Seventeen-Level Inverter Formed by Cascading Flying Capacitor and Floating Capacitor H-Bridges," in IEEE Transactions on Power Electronics, vol. 30, no. 7, pp. 3471-3478, July 2015.

- On-Cheong Mak and A. Ioinovici, "Switched-capacitor inverter with high power density and enhanced regulation capability," in IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 45, no. 4, pp. 336-347, April 1998.

- Y. Hinago and H. Koizumi, "A Switched-Capacitor Inverter Using Series/Parallel Conversion With Inductive Load," in IEEE Transactions on Industrial Electronics, vol. 59, no. 2, pp. 878-887, Feb. 2012.

- 17. E. Babaei and S. S. Gowgani, "Hybrid Multilevel Inverter Using Switched Capacitor Units," in IEEE Transactions on Industrial Electronics, vol. 61, no. 9, pp. 4614-4621, Sept. 2014.

- 18. Y. Ye, K. W. E. Cheng, J. Liu and K. Ding, "A Step-Up SwitchedCapacitor Multilevel Inverter With Self-Voltage Balancing," in IEEE Transactions on Industrial Electronics, vol. 61, no. 12, pp. 6672-6680, Dec. 2014.

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 11, Iss 12, Dec 2022

- 19. J. Liu, K. W. E. Cheng and Y. Ye, "A Cascaded Multilevel Inverter Based on Switched-Capacitor for High-Frequency AC Power Distribution System," in IEEE Transactions on Power Electronics, vol. 29, no. 8, pp. 4219-4230, Aug. 2014.

- 20. E. Zamiri, N. Vosoughi, S. H. Hosseini, R. Barzegarkhoo and M. Sabahi, "A New Cascaded Switched-Capacitor Multilevel Inverter Based on Improved Series–Parallel Conversion With Less Number of Components," in IEEE Transactions on Industrial Electronics, vol. 63, no. 6, pp. 3582-3594, June 2016.

- R. Barzegarkhoo, H. M. Kojabadi, E. Zamiry, N. Vosoughi and L. Chang, "Generalized Structure for a Single Phase Switched-Capacitor Multilevel Inverter Using a New Multiple DC Link Producer With Reduced Number of Switches," in IEEE Transactions on Power Electronics, vol. 31, no. 8, pp. 5604-5617, Aug. 2016.

- 22. M. Saeedian, S. M. Hosseini and J. Adabi, "Step-up switched-capacitor module for cascaded MLI topologies," in IET Power Electronics, vol. 11, no. 7, pp. 1286-1296, 19 6 2018.

- 23. R. Barzegarkhoo, M. Moradzadeh, E. Zamiri, H. Madadi Kojabadi and F. Blaabjerg, "A New Boost Switched-Capacitor Multilevel Converter With Reduced Circuit Devices," in IEEE Transactions on Power Electronics, vol. 33, no. 8, pp. 6738-6754, Aug. 2018.

- 24. T. Roy, P. K. Sadhu and A. Dasgupta, "Cross-Switched Multilevel Inverter Using Novel Switched Capacitor Converters," in IEEE Transactions on Industrial Electronics, vol. 66, no. 11, pp. 8521-8532, Nov. 2019.

- M. Saeedian, S. M. Hosseini and J. Adabi, "A Five-Level Step-Up Module for Multilevel Inverters: Topology, Modulation Strategy, and Implementation," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 4, pp. 2215-2226, Dec. 2018.

- 26. J. Liu, X. Zhu and J. Zeng, "A Seven-level Inverter with Self-balancing and Low Voltage Stress," in IEEE Journal of Emerging and Selected Topics in Power Electronics. doi: 10.1109/JESTPE.2018.2879890.

- 27. W. Peng, Q. Ni, X. Qiu and Y. Ye, "Seven-Level Inverter with SelfBalanced Switched-Capacitor and Its Cascaded Extension," in IEEE Transactions on Power Electronics. doi: 10.1109/TPEL.2019.29047.