# Low Power VLSI Intelligent Circuits Design Methodologies

#### Prof. Lalita K. Wani

Assistant Professor, Bharati Vidyapeeth's College of Engineering, Lavale, Pune, MH, India. Lalita.wani@gmail.com

# Prof. (Dr.) Reena Singh

MES's, Pillai HOC College of Engineering & Technology, Rasayani Taluka Panvel, Dist, Navi Mumbai, Maharashtra 410207, India. dr.rsingh2014@gmail.com

## Prof. (Dr.) B.K. Sarkar

MES's, Geh Research, Panvel, Dist, Navi Mumbai, Maharashtra 410207, India. dr.bksarkar2003@yahoo.in

#### **Abstract:**

Low power has arisen as a chief subject in this day and age of hardware ventures. Power dispersal has turned into a significant thought as execution and region for VLSI Chip plan. With contracting innovation lessening power utilization and over all power the board on chip are the vital moves underneath 100nm because of expanded intricacy. For some plans, streamlining of force is significant as timing because of the need to lessen bundle cost and expanded battery duration. For power the board spillage current additionally assumes a significant part in low power VLSI plans. Spillage current is turning into an undeniably significant part of the all out power dispersal of incorporated circuits. This paper portrays about the different procedures, strategies and power the executive's methods for low power circuits and frameworks. Future difficulties that should be met to plans low power superior execution circuits are additionally talked about.

**Keywords:** Power Dissipation, low power, process nodes, leakage current, power management.

#### INTRODUCTION

The benefit of using a mix of low-power parts related to low-control plan procedures is more significant now than any other time. Prerequisites for lower power utilization keep on expanding essentially as parts become battery-fueled, more modest and require greater usefulness. In the past the central issues for the VLSI fashioners was region, execution and cost. Power thought was the auxiliary concerned. Presently a day's power is the essential worried because of the surprising development and progress in the field of individualized computing gadgets and remote correspondence framework which request high velocity calculation and complex usefulness with low power utilization. The inspirations for lessening power utilization contrast application to application. In the class of miniature controlled battery worked convenient applications, for example, cells, the objective is to keep the battery

lifetime and weight sensible and bundling cost low. For superior execution convenient PCs, for example, PC the objective is to diminish the power scattering of the hardware piece of the framework to a point which is about portion of the complete power dispersal.

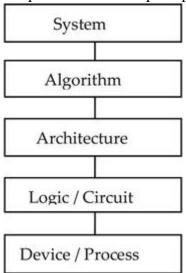

FIG.1: Low Power VLSI Intelligent Circuits Design Methodologies Flow Chart.

At last for the superior exhibition non battery worked framework, for example, workstations the general objective of force minimization is to diminish the framework cost while guaranteeing long haul gadget unwavering quality. For such elite execution frameworks, process innovation has driven capacity to the front to all variables in such plans. At process hubs under 100 nm innovation, power utilization because of spillage has joined exchanging movement as an essential power the board concern.

The upside of using a mix of low-power parts related to low-drive plan strategies is more significant now than any other time in recent memory. Necessities for lower power utilization keep on expanding altogether as parts become battery-controlled, more modest and require greater usefulness. In the past the main issues for the VLSI fashioners was region, execution and cost. Power thought was the optional concerned. Presently a day's power is the essential worried because of the noteworthy development and outcome in the field of individualized computing gadgets and remote correspondence framework which request high velocity calculation and complex usefulness with low power utilization.

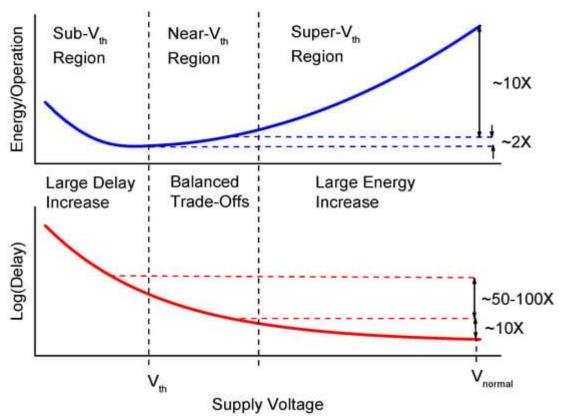

Fig.2: Low Power VLSI Intelligent Circuits Design Methodologies Graph.

The inspirations for diminishing power utilization contrast application to application. In the class of miniature fueled battery worked convenient applications, for example, phones, the objective is to keep the battery lifetime and weight sensible and bundling cost low. For superior execution convenient PCs, for example, PC the objective is to decrease the power dispersal of the hardware part of the framework to a point which is about portion of the complete power scattering. At last for the elite presentation non battery worked framework, for example, workstations the general objective of force minimization is to lessen the framework cost while guaranteeing long haul gadget dependability. For such elite execution frameworks, process innovation has driven capacity to the front to all elements in such plans. At process hubs under 100 nm innovation, power utilization because of spillage has joined exchanging action as an essential power the board concern.

## Need for low power plan

Power dissemination is the primary requirement with regards to convey ability. Consequently, dealing with the framework's complete power consumption is fundamental. Limiting the general power utilization in such gadgets is fundamental since it is favourable to take advantage of the run time with least potential necessities on weight, battery duration and size owed to batteries. In this manner, in compact gadgets, 'the low power configuration is the most conclusive element to think while planning framework on chip. Typically, portable clients request extra elements and delayed battery duration at a lower cost. Practically 70% of clients search for longer talk time and backup time as key element for cell phones. One of the top administrator prerequisites in 4G is Power proficiency. Clients generally search for more Thus, plan is vital in low power utilization gadgets.

modest, trim and effortless cell phones. This is the need of elevated degrees of silicon reconciliation in current cycles, yet modern cycles have naturally higher power extravagance.

#### **Power demonstrating**

Various power parts and their result should be recognized to diminish power utilization of specific circuit. Out of two power scattering types, the most extreme power dispersal connects with top immediate current and the subsequent kind is normal power dissemination. Because of electrical cable obstruction, top flow influences the commotion in supply voltage. This causes warming of gadget and thus brings about execution corruption. With a view on battery duration time, this typical power scattering turns out to be more significant. The three significant power dissemination parts are [1].

# Plan boundary

The low power configuration work basically centers on assessing the unique power dispersal. Previously, the central issue of the originator was about region, speed and cost. The optional significance was accommodated power contemplations. As of late, power has become as the essential plan thought. A few variables add to this pattern like the development of individualized computing gadgets, for example, convenient work areas, sound and video-based interactive media items and remote correspondence frameworks which request high velocity calculation and complex usefulness with low power utilization [6]. So there is areas of strength for a for power utilization decrease to diminish bundling and cooling cost and further develop item dependability. At the point when the objective is a low power application, a power analyser/assessor positions the different plan viewpoints, in this manner helps in choosing the one that is possibly more compelling from the power outlook.

## The Role of Technology Selection

Legitimate innovation determination is one of the vital parts of force the board [1]. The objective of every innovation headway is to further develop execution, thickness, and power utilization. The regular methodology in fostering another age of innovation is to apply consistent electric-field scaling. Process planners scale both the applied voltage and the oxide thickness to keep up with a similar electric field [13, 16].

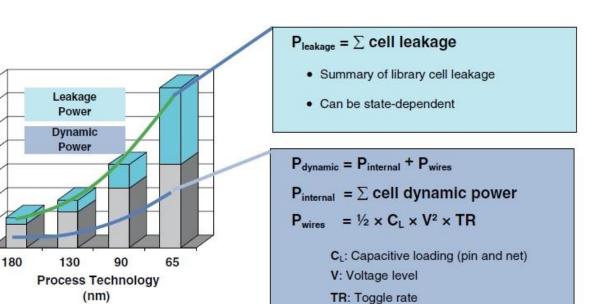

FIG.3: Low Power VLSI Intelligent Circuits Design Methodologies Process.

This approach decreases power by around half with each new innovation hub In any case, as the voltage gets more modest, the edge voltage likewise should downsize to meet the presentation focuses of that innovation.

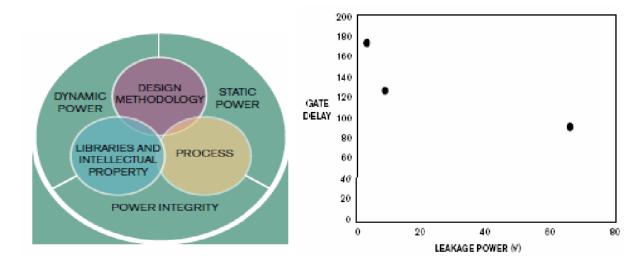

Fig.4: Low Power VLSI Intelligent Circuits Design Methodologies Cycle.

This scaling sadly builds the sub edge current and consequently the spillage power. To conquer this imperative, process designs never again apply steady field scaling for cycles of 65 nm or more modest; all things considered, they utilized a more summed up type of scaling. Since it is difficult to improve an innovation for both execution and spillage without a moment's delay, every innovation for the most part has two variations. One variation goes for the gold, and different goes for low spillage. The essential distinctions between the two are in the oxide thickness, supply voltage, and edge voltage.

#### **Results**

Analysts gaze at the plan of low power gadgets as they are administering the present hardware ventures. In VLSI circuits, power scattering is a basic plan boundary as it assumes a fundamental part in the presentation assessment of the battery worked gadgets especially utilized in biomedical applications. The diminishing in chip size and expansion in chip thickness and intricacy raise the trouble in planning better execution low power consuming framework on a chip. Further, in general power the executives on a chip is turning into a major test under 100 nm hub in light of its expanded plan intricacy. Moreover, spillage current likewise assumes an imperative part in Power the executives of low power VLSI gadgets. In sub-micron innovations, spillage and dynamic power utilization is turning into a fundamental plan boundary as it is scattering a significant part of the all out power utilization. To build the battery duration of convenient gadgets, spillage and dynamic power decrease is arising as an essential objective of the VLSI circuit plan. This paper gives an understanding about the different philosophies, methodologies and power the executive's strategies to be utilized for the plan of low power circuit based frameworks.

#### **CONCLUSION**

The requirement for lower power frameworks is being driven by many market portions. Sadly planning for low power adds one more aspect to the all-around complex plan issue and the plan must be streamlined for power as well as Execution and Region. All in all different issues and significant difficulties in regards to low power plans are: - 1 Innovation Scaling: It relates with the accompanying variables like: Capacitance per hub decreases by 30%, Electrical hubs increments by 2X, Kick the bucket size develops by 14% (Moore's Regulation), Supply Voltage diminishes by 15% and Recurrence Increments by 2X. To meet these issues moderately 2.7 X dynamic power will increment. 2 Spillage power: To satisfy recurrence need VT will be scaled which results high spillage power. A low voltage/low limit innovation and circuit configuration approach, focusing on supply voltage around 1V and working with decreased edges. 3 Unique power the executive's strategies, shifting inventory voltage and execution speed as per the action estimation. 4 Low power interconnect, utilizing advance innovation, diminished swing or movement approach. 5 Improvement of force cognizant strategies and devices for conduct blend, rationale combination and design enhancement. 6 Power saving strategies that reuse the sign energies utilizing the adiabatic exchanging chiefs rather them dispersing them as an intensity and promising in specific applications where speed can be exchanges for low power.

#### **REFERENCES**

- [1] Michael Keating, David Flynn, Robert Aitken, Ala Gibsons and Kaijian Shi, "Low Power Methodology Manual for System on Chip Design", Springer Publications, New York, 2007. [2] Creating Low-Power Digital Integrated Circuits the Implementation Phase, Cadence,

- 2007.

- [3] Liu, Weidong, Xiaodong Jin, Xuemei Xi, James Chen, Min-Chie Jeng, Zhihong Liu, Yuhua Cheng, Kai Chen, Mansun Chan, Kelvin Hui, Jianhui Huang, Robert Tu, Ping K Ko, and Chenming Hu, BSIM3v3.3 MOSFET Model User's Manual, Department of Electrical Engineering and Computer Sciences, University of California-Berkeley, 2005.

- [4] Glasser, Lance A, and Daniel W Dobberpuhl, TheDesign and Analysis of VLSI Circuits, Addison-Wesley Publishing Co, 1985.

- [5] Shekar Borkar, "Design Challenges of Technology Scaling," IEEE Micro, July/August 1999, pg 23.

- [6] T. Inukai, et.al, "Boosted Gate MOS (BGMOS): Device/Circuit Cooperation Scheme to Achieve Leakage Free Giga- Scale Integration," Proc. CICC 2000, pp.409-412.

- [7] F. Hamzaoglu and M. Stan, "Circuit-Level Techniques to Control Gate Leakage for sub 100nm CMOS," Proc. ISLPED, pp. 60-63, Aug. 2002.

- [8] Y. Yeo, et.al, "Direct Tunneling Gate Leakage Current in Transistors with Ultrathin Silicon Nitride Gate Dielectric," IEEE Electron Devices Letters, vol.21, no.11, pp. 540-542, Nov.2000.

- [9] S. Mutoh, et.al, "1-V Power Supply High-Speed Digital Circuit Technology with Multi-Threshold Voltage CMOS,"IEEE Journal of Solid State Circuits, vol. 30, no. 8, pp. 847-854, Aug. 1995.

- [10] M. Alidina, j. Monterio, S. Devadas, A. Ghosh and M. Papaefthymiou. "Precomputation -based Sequential logic optimization for low power" In Proceedings of the 1994 International Workshop on Low Power Design, pages 57-62, April 1994.

- [11] Anand Iyer, "Demystify power gating and stop leakage cold", Cadence Design Systems, Inc.

- [12] De-Shiuan Chiou, Shih-Hsin Chen, Chingwei Yeh, "Timing driven power gating", Proceedings of the 43rd annual conference on Design automation, ACM Special Interest Group on Design Automation, pp.121 - 124, 2006.