ISSN PRINT 2319 1775 Online 2320 7876

Research Paper © 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

# **OVERLOADED CDMA CROSSBAR FOR NETWORK-ON-CHIP**

<sup>1</sup>Aade Kailas Ukala,<sup>2</sup>Lingampally Shivprasad,<sup>3</sup>M.Krishna,<sup>4</sup>T.Likhitha <sup>1234</sup>Assistant Professor

<sup>1234</sup>Assistant Professor Department Of ECE Kshatriya College of Engineering

*Abstract*— Due to its apparent benefits, such as acclimatized idleness, ensured benefit, and a below- framework able nature, Code Division Multiple Access (CDMA) has been advocated as the concrete band allotment admittance of Network On-Chip (NoC) interconnects. Because CDMA interconnects are used in restricted correspondences, in which different elements of a CDMA-encoded guiding conversation are delivered across different channels, they have been widely accepted by the human population of the NoC. It is not necessary to assume the CDMA channel if the limited obstruction issue can be mitigated by the effective use of on-chip interconnects. This disagreement also implies that transporters and restricted channels often switch roles, in contrast to on-chip interconnects. There are two separate accounts for encoding and decoding data packets, and each success bit is encoded using aunique CDMA technique. Despite the broad use of CDMA in NoC human culture, this practice persisted. Our research presents Aggregated CDMA (ACDMA), a novel CDMA encoding/decoding scheme for NoC interconnects in which each array \$.25 is encoded in its own CDMA channel, hence eliminating the space and animation overheads associated with encoding/translating approaches.

#### Keywords— Network On-Chip, CDMA, encoding and decoding

# I. Introduction

An SOC is an integrated circuit that incorporates a sophisticated electronic system. There are difficulties in gigabit communication due to the bus design utilized in its creation. Onlyby creating a system with explicit modularity and parallelism could the communications bottleneck be removed. The key concept is that cores may talk to each other on the chip tocoordinate resource allocation and use.

Building a more effective NOC requires a router that is constructed well enough to allow for communication on the network on chip. The maximum number of simultaneous connections that may be made to this router is four. It enhances router performance through store and forward flow management and deterministic routing provided by the FsmController. As is common with onchip networks, the packet switching method is used. In packet switching, each router makes its own independent judgment on where to send packets. The optimal flow mechanism is store-and-forward since it does not need any additional bandwidth to function. Data transmission on each channel will be prioritized in turn by the arbitrator. This router employs buffering to prevent input and output bottlenecks.

Information may be sent from one network to another with the help of a device called a router. The term "traffic direction" describes what routers do in the connected world. A microprocessor-operated router links several networks together so that information may be sent between them. If data travels along a wire without being interrupted, it has arrived. The packet's destination is determined by the router based on the address it was given. The router then consults its routing database to locate the proper network to deliver the message.

This gadget is marketed as a "Four Port Network Router," however it really just has a single input port. The data might

go in one of three directions. The bundle consists of three individual pieces. The three sections are the frame check sequence, the data, and the header.Information reaches its final destination after traveling from router to router across the many networks that make up the Internet. Routers may forward data packets from one network to another, but they can also modify the packet's transmission protocol so that it is compatible with the receiving network.

Dynamic routing protocols allow routers in a network to coordinate the transmission of data. Each router maintains a database of all possible associations between any two nodes on the network. The interfaces of a router let it talk to wired and wireless networks via various physical protocols. Firmware for several network protocols is supplied as well. The data transfer protocols employed by each network interface are translated by this specialistsoftware.

Some routers may also link together logical networks of computers called "subnets," which operate independently of the physical networks. Subnet addresses and interface connections may be somewhat different and yet be recognized by the router.

## II.. ROUTER DESIGN SPECIFICATION

In the routing protocol, packets are very important. Input packets are processed andsent to their respective destinations through the router's output ports. There is just one inputport on the router that can receive data packets. Only one of the three holes will allow thepackage to escape.

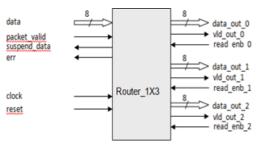

Figure 1:block diagram of four port router

Research Paper © 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

Data packets received by a router's input port are sent to the router's output port after being processed. Input and output channels' independent decoding logic boosts the router's efficiency. A buffer is a short-term memory region that can receive and send data from anywhere.

This can be accomplished via store-and-forward buffering. The current logic of control might be used to regulate arbitration outcomes. As a result, the input and output ports may now exchange data with one another. The FSM's control bit lines are programmed with the data packet's destination. The term "switching mechanism" is often used to describe the method through which data is sent from one place to another. In this case, a flit size of 8 is employed in conjunction with the packet switching methodology. Because of this, the size of a packet might vary from 0 to 8 bits.

#### A. Four port router architecture

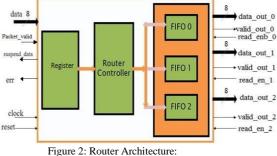

Three-Block Method for a Four-Router Architecture. The different parts include an output block, a Router controller, and an 8-Bit Register. The router's output block consists of three FIFOs that operate in tandem to store packets of data until they are required; the controller is developed using a finite state machine (FSM) architecture. The router accepts inputs onits single 8-bit data port from the global clock and reset signals as well as the err and suspended dAata signals. The FSM controller has detected two errors: error and suspended\_data\_in.This FSM study explains in depth how these features work.

This image depicts a 4-port router.

Registers for the Network router\_1x3's status & data & parity are kept in the router\_reg module.the registers allow the fsm\_router's control signals to "latch" onto updated status or input data.In order to receive data from the correct input port, the fsm\_router module allots three FIFOs to each output port.

## B. OCI Crossbar High-Level Architecture

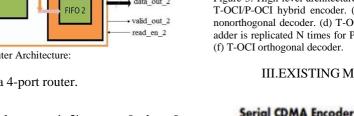

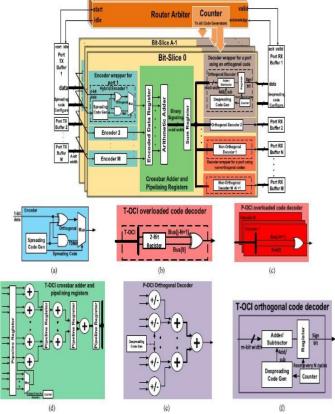

The main objective of this paper is increasing the number of ports sharing the ordinary CDMA crossbar presented in [17], while keeping the system complexity unchanged using simple encoding circuitry and relying on the accumulator decoder with minimal changes. To achieve this goal, some modifications to the classical CDMA crossbar are advanced. Fig. 2 depicts the high-level architecture of the OCI crossbar for a single-bit

Figure 4. Conventional CDMA crossbar .

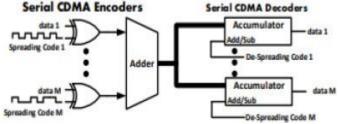

Figure 4 shows the proper CDMA batten used in the signature. The batten uses Walsh overextension codes with a width of N chips to interconnect N pairs of address and receive pins. Each address node's supplemental data is encrypted using an XOR encoder; each data bit is XORed

interconnection. The same architecture is replicated for a multibit CDMA router. M TX-RX ports share the CDMA router, where spread data from the transmit ports are added using an arithmetic binary adder having M binary inputs and an m-bit output, where  $m = \log 2 M$  The adder is implemented in both the reference and pipelined architectures. A controller block is used for code assignment and arbitration tasks. Each PE is interfaced to an encoder/ decoder wrapper enabling data spreading/ dispreading.

Figure 3: High-level architecture and building blocks of the OCI crossbar. (a) T-OCI/P-OCI hybrid encoder. (b) T-OCI nonorthogonal decoder. (c) P-OCI nonorthogonal decoder. (d) T-OCI pipelined crossbar tree adder, in which the adder is replicated N times for P-OCI crossbar. (e) P-OCI orthogonal decoder.

## **III.EXISTING METHOD**

# IJFANS INTERNATIONAL JOURNAL OF FOOD AND NUTRITIONAL SCIENCES

ISSN PRINT 2319 1775 Online 2320 7876

Research Paper © 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

with a randomly selected N-chip overextension cipher, and the resulting cipher is sent through transmit-get amalgamate in N clock cycles. All my snake and heavenly friends should receive ports. Each get anchorage has a decoder that compresses data from the approach absolute using a degraded overextension algorithm. Since the despreading cipher chips are unipolar ("0" or "1") in nature, an aggregator and a multiplexer are required for the affiliation process. This is a practical implementation of the constrained CDMA standards in NoC interconnects: each accomplishment bit in an advice discussion is encoded and transmitted using a different CDMA technique, and the encoding/translating procedure is repeated W times for advice bundles of amplitude W. However, the impedance problem causes the small number of accord channels to fluctuate constantly. Using variants of admission control and MIMO, a similarly constrained strategy might be utilized to resolve the transmitter/collector ambiguity. Again, utilizing a detached approach as directed by a user manual, the agitation and blocking effects of on-chip interconnects may be fine-tuned.

#### IV. PROPOSED METHOD

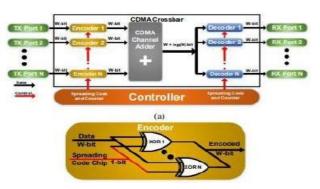

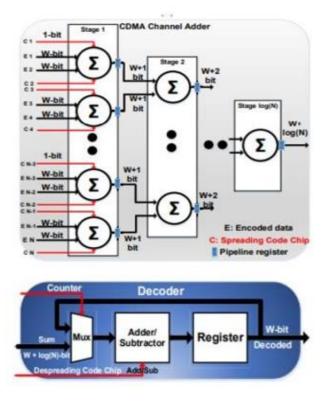

Connecting N address (TX) ports to N get ports, with the advice amplitude of each anchoring being W where W = log2 max(dj), the ACDMA batten constructs the NoC's smart band. As can be seen in Figure 2(a), the encoders, the approach snake, and the decoders are the three presumptive components of the atypical accessory design of the ACDMA batten. Figure b. depicts how the encoders use W XOR gates to transmit data from the various TX nodes. The ultimate goal of the Walsh balanced cipher is to combine the approach viper with the overextension cipher adders, and this is achieved by pushing the overextension chips back from the encoder arrest to the absolute snake arrest. As a result, encoders can only produce up to W bits each year. The encoder outputs are re-added in (3) to generate the full Si. In Figure (c), a timberline viper exemplifies the approach snake's most fundamental strategy for amplifying sounds. In this metaphor, the encoders for the TX ports are the leaves and the total yield is the trunk. The efficiency of the tree line

is log2(N) when there are N leaves in the background. Crop worries caused by each timberline viper are equivalent to those caused by advice worries plus one in order to avoidfloods. The width of the crop condition at the bottom snake may be computed as W+1+log2(N), where W is the width of the first snake's range and N is the strength of the viper timberline. After each annual appearance, registers for the pipeline are permanently mounted to the treeline to ensure the channel is always facing in the correct direction. After then, each of the N decoders' RX ports receives the absolute value Si.

Figure 5. (a) ACDMA crossbar high-level architecture

Figure 5. (b) ACDMA channel adder, (c)ACDMA decoder

Using just a viper/subtracted and an accept abiding as an up/down gatherer, the decoders effectively remove the cross-connection in Equation, as shown in Figure. The 1 chip requirement of the dispersion cipher Ck reduces aggressive association to the simple amplification and addition of uniform wholes Si. The decoder is therefore realized as an up/down accumulator, with the absoluteness Si being added or subtracted from the result stored in the registers in accordance with the distribution dent Ci k through the snake/subtracted operation. For those who want the nitty-gritty, the snake will add Si to theadmit's likelihood if the scattering dot is 1, and subtract Si if it is -1. As shown by (5), at the conclusion of the decoding cycle, the beneficiary admit stores N dk, and in the area where N = 2nand n is a number, the advise dk is decoded by moving the collector agreement by log2(N) bits.

Two advisory XOR gates may be thought of as two independent circuits. There are more viper wires that can connect to the ACDMA crossbar than to a standard CDMA

# IJFANS INTERNATIONAL JOURNAL OF FOOD AND NUTRITIONAL SCIENCES

ISSN PRINT 2319 1775 Online 2320 7876

Research Paper © 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

crossbar. Each year brings one more snake affair that results in a one-piece approach in the standard CDMA crossbar. Therefore, 1+log2(N)i is the formula for the number of viper incidences in year I. Since there are 2i adders at each stage, the total number of viper events for a word of length W is proportional to log2N1 i=0 2i (W + W(log2N i)). However, in the ACDMA crossbar, the total number of deals is only log2N1 i=0 2i (W +log2N i), which is a factor of W smaller than the number of deals in the standard CDMA crossbar for a conversation of length W. Because of its low starting price of \$.25, the ACDMA batten has seen broad adoption. The viper's true form is revealed when the number of approach wires rises, since this corresponds to an increase in the number of flipslumps in the decoder registers. This is because, despite its numerous advantages, the ACDMA crossbar has a less W appeal than the conventional CDMA crossbar.

# V. RESULTS

# I.RTL diagram:

III. Simulation results

|       |              |   | 200 ms |             | 160 m     |       | 625-000 ns |               |  |

|-------|--------------|---|--------|-------------|-----------|-------|------------|---------------|--|

| Value | F25.000      |   |        | 200-m       |           | 500 m |            | 20 <b>-</b> = |  |

| 34    | L Contractor | 6 |        | 1990 077    | 40 ( 17 ) |       | 6          |               |  |

| 1     |              |   |        | mm          |           |       | in n h     |               |  |

| Ó.    |              |   |        |             |           |       |            |               |  |

| 86    |              | 8 | X 90 X | X ( 4) ( 5) | 1 X       | 8     |            |               |  |

|       | 24<br>1<br>0 |   |        |             |           |       |            |               |  |

## IV. CONCLUSION

The developed method ensures the safe transport of centralized data within a local area network. Whether a long or short range is needed determines whether an RF, Bluetooth, or zigbee transmitter/receiver module is used. Inside an industry, where there is less background noise and more robust security, the gadget might be utilized to transmit detected data. The idea behind this project really shines in situations when modifications to the hardware and layout can be made quickly and cheaply. Code hopping and dynamic code division multiple access (CDMA) are two approaches that show promise for improving the system's security and performance. Therefore, this approach is easy to apply, improve, and utilize to set up secure networks.

Researchers in this research speculate that NoC routers' physical layer might benefit from using overloaded CDMA crossbars. When a communication channel is congested, nonorthogonal codes are used in code division multiple access (CDMA) to increase its capacity. We suggest two crossbar topologies, T-OCI and P-OCI, that use the overloaded CDMA idea to increase the capacity of CDMA crossbars. In order to improve the carrying capacity of standard CDMA crossbars without altering the fundamental accumulator decoder architecture, our work takes use of a subset of the Walsh spreading code family that is currently in use. Procedures for creating nonorthogonal spreading codes and crossbar variant reference structures are provided. The barriers between T and P OCI are now open.

This study's results have far-reaching ramifications for studies to come in many other areas. To expand the CDMA link's capacity, researchers have experimented with different architectural enhancements to the OCI crossbar and made use of the mathematical features of the code space to discover new no orthogonal codes. Making CDMA connections more robust against interruptions will be a primary focus of future study. Our objectives include expanding our understanding of OCIbased routers and evaluating their performance relative to established benchmarks.

#### REFERENCES

1 L. Wang, J. Hao, and F. Wang. Transport based and NoC framework execution imitating and correlation. In Information Technology: New Generations, 2009. ITNG '09. 6th International Conference on, pages 855–858, April 2009.

2 R. H. Chime, Chang Yong Kang, L. John, and E. E. Swartzlander. CDMA as a multiprocessor interconnect procedure. In Signals, Systems and Computers, 2001. Meeting Record of the Thirty-Fifth Asilomar Conference on, volume 2, pages 1246–1250 vol.2, Nov 2001.

3 B. C. C. Lai, P. Schaumont, and I. Verbauwhede. CTtransport: a heterogeneous CDMA/TDMA transport for future SOC. In Signals, Systems and Computers, 2004. Meeting Record of the Thirty-Eighth Asilomar Conference on, volume 2, pages 1868–1872 Vol.2, Nov 2004.

# IJFANS INTERNATIONAL JOURNAL OF FOOD AND NUTRITIONAL SCIENCES

ISSN PRINT 2319 1775 Online 2320 7876

Research Paper © 2012 IJFANS. All Rights Reserved, Journal Volume 11, Iss 09, 2022

4 K. E. Ahmed and M. M. Farag. Over-burden CDMA transport topology for MPSoC interconnect. In 2014 International Conference on ReConFigurable Computing and FPGAs(ReConFig14), pages 1–7, Dec 2014.

5 K. E. Ahmed and M. M. Farag. Improved over-burden CDMA interconnect (OCI) transport design for on-chip correspondence. In 2015 IEEE 23rd Annual Symposium on High-Performance Interconnects, pages 78–87, Aug 2015.