# ISSN PRINT 2319 1775 Online 2320 7876

Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

# UTILIZING BUILT-IN SELF-TEST ARCHITECTURE FOR WEIGHTED PSEUDO RANDOM TEST PATTERN GENERATOR IMPLEMENTATION

1Mrs. K. Vanisree, 2Duri Virajini, 3Thatiparthy Mounika, 4Sangeetha Balne

1Assistant Professor&HOD,2,3,4Assistant Professor

Department of ECE

Samskruti College of Engineering and Technology, Hyderabad

*Abstract* -Expanded chip capabilities is a notable need as submicron technology develops. Due to the current generation's mass production of ICs, thorough testing is necessary to separate the good chips from the poor. Verification Engineers must comprehend the operation of the chip in order to perform a comprehensive verification and find any flaws in the product. Because they demand a significant time investment and circuit complexity, conventional testing methods are not adequate for the current generation. As a result, it becomes necessary to automatically create test patterns with a high level of variability in between them. The randomness that is employed to generate the test pattern is provided by Galois fields. A weighted test pattern generator has also been used.

Keywords: test pattern generator, pseudorandom TPG, circuit being tested, integrated self-test

# I. INTRODUCTION

Current innovation has focused on growing low-power frameworks for especially vast scope becoming a member of (VLSI) speedy plans. Therefore, some plan techniques [1] have been completed to alleviate compromises among execution, strength, and vicinity. Some methodologies have concentrated on low-power dispersal throughout BIST normal mode operations rather than test mode operation [1].

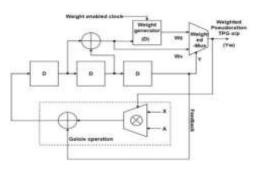

Figure 1. An example of a conventional pseudo random TPG

During the BIST normal mode operation, the replacing motion with inside the output chains and check information stress using the suitable TPG are crucial. Additionally, this finding out should be achieved with immoderate dependability and responsiveness in semiconductor designs. Figure1 illustrates an example of a conventional [2].The partner supervisor planning the survey of this composition and helping it for distribution changed into Wu-Shiung Feng.

# A. Pseudorandom TPG

The TPG contains of the affiliation of length n shift registers and input seed bits of  $a_0$ ,  $a_1$ ,  $a_2$ ..., an. In moderate of the n<sup>th</sup> cycle of the shift sign up, the  $(I - 1)^{th}$  clock

# ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

cycle[3] is refreshed constantly through manner of method of the  $(n_1)^{th}$  cycle of the shift sign up and the I<sup>th</sup> clock cycle. The TPGs make use of important level of parallelism to perform excessive cross back records in several useful packages. The TPG [1] direct capability is executed through way of method of the outset complete signal and the data seed bits. Its direct functionalities are implemented in many programs like plane frameworks, cockpit frameworks, scientific frameworks, sound and video frameworks, and power age and dispersion frameworks.

A TPG carries of deterministic, complete, pseudorandom, pseudorandom weighted [4] blended and mode vields. The pseudorandom weighted out placed issued to carry out better problem inclusion in numerous BIST systems. The weighted pseudorandom TPG suggests genuine irregularity and repeatable examples in all clock cycles. Regularly, it requires one seed bit to deliver one check format for 'n' forms of the checking ease within side the check according to take look at BIST[2], in which 'n' is the scan chain cycle. The most modern overview diminished the switching activity all through test shift cycles. Furthermore, the TPG permits the programmed preference of weighted obstacles to perform its low power. The weighted pseudo arbitrary TPG techniques and their execution in, can in true modifications. lessen replacing the Nonetheless, the techniques, incorporated extra XOR adjustments the various shift registers [3], it consumed extra power and location. The BIST necessities need to be in fashionable zero in at the better short coming inclusion and the lesser weighted changing movement with lower power.

Figure 2. (a) spare TPG

Figure 2. (b) Spare TPG

To accomplish those requirements, methodologies can be used. One is to regulate the circuit plan of the weighted TPG [4]. The distinctive is to remember more machines for the weighted TPG. The present work describes every different pseudorandom weighted TPG is advanced the use of extra machine. Also, higher shortcoming inclusion is accomplished as a long way as getting rid of change remove deficiencies using check thing addition. The check focuses are embedded for every NAND entryway design of the general plan region. The proposed approach is composed of purchasing and promoting weighted

## ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

check examples to the output chains the use of a phase shifter.

The buying and promoting of the weighted examples taken into consideration for picking the earlier output chains with lesser region is contrasted and that of the others scan chains [5]. The weighted examples are consequently carried out with all the output chains of BIST layout. This dispenses with the problems at a predefined vield and further improves the fault coverage. The TPG likewise in addition develops its speedy changing motion due to its selected weighted designs and reduces its ordinary checking and catching energy usage in some unspecified time in the future of BIST check consistent with observe. The proposed TPG is planned using intent door strategies and finished in precise test according to observe BIST designs.

# II. EXISTING WEIGHTED PSEUDORANDOM TPGS

Figure 3. Existing 3-bit weighted pseudorandom TPG

The primitive polynomial chosen for the now not set in tone with the resource of the use of the even or ordinary faucet bits from the register. By and large, crude polynomials are carried out for growing pseudorandom designs. On the off risk that the faucet bit groupings of a n-digit TPG [5] are n, m, k, l, ..., 0, then the co primes of the faucet numbers, like n-n, n-m, n-k, n-l, ..., n-0, will likewise produce the pseudorandom TPG yield. Utilizing this concept, the TPG can create a notable length of pseudo critical seeds. In Figure 2, the darkish line way that the supply TPG yields pseudorandom designs, and the blue line.

factors show the greater system implemented for producing the weighted pseudorandom designs [6].

The existing weighted repetitive TPG approach in Figure 3 makes use of each duplication device or elements. The hardware redundancy duplicates its functions into double modular redundancy, triple modular redundancy and so on. This may be completed through copying the greater for the deliver TPG tool therefore configuration, removing the arbitrary example steady short comings. Be that due to the fact it may, the device overt repetitiveness TPG accomplishes super execution factors; it needs to be reducible with inside the device above [3]. The time overt repetitiveness is finished using the one of a kind time measures rather than the tool utilizing the offbeat clock values going from "0" to "1". In any case, a similar interest is carried out making use of several time elements for the weighted examples. This

# ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

method distinguishes numerous secure deficiencies at some point of several clock cycles.

The existing weighted 3-bit pseudorandom TPG maximum details weighted applied for generating the examples associated with, the manage bits for the multiplexer (Mux) [6]. The greater tool is likewise used to offer the reseeding quantities expected for the check example to differentiate their faults. The Mux with inside the extra hardware identifies informs the information seeds and to manipulate bits even as the regular weight input Win passes the weighted examples to a end result. In any case, this recalls a large place above for the can woodland plan of the BIST engineering. This can likewise be carried out for the critical path delay, scanning power testing capture power weighted and reseeding technique.

Later, more sophisticated TPG techniques are introduced, as illustrated in Figure3, to circumvent the restrictions of these TPGs. These strategies use identical TPGs and records overt repetitiveness to focus on the test pattern's weight [2]. Barry et al. claim (Figure 3) that the TPG strategy makes use of a Mux a few of the D flip flops, where the signal is planned to be managed to the underlying enormous state of the weighted instance. In the end, the suggested TPG incorporates the requirements of the current works. It presents a valid scenario for producing weighted examples for a larger seed bit with significantly less power and placement above. Essentially, this strategy must guarantee low power interest during the full test for each study.

III. WEIGHTED PSEUDORANDOM TPG USING THE GALOIS OPERATION WITH A PHASE SHIFTER.

**Figure 4.** Proposed 3-bit weighted pseudorandom TPG.

Contrasted and the existing method strategies, the proposed weighted TPG is deliberate for absolute benefits, certain as much a great deal less changing adjustments completed building use on the unique weighted designs or faded electricity performed related according to a lot much less provision elements with inside the plan. This decreases the provision over or similarly develops the challenge inclusions with inside the BIST [8]. The TPG approach displayed within is the proposed TPG, which includes the Galois operation and addition hardware for weighted pattern generation. The Galois pastime with inside the proposed TPG is confirmed along the

# ISSN PRINT 2319 1775 Online 2320 7876

Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

resource regarding the use of the black dashed line expects ordinary pseudo critical seeds (A, X). Nonetheless, the regular truss portions may additionally remain prolonged construction uses concerning similar subset on introductory essential seeds [9]. The bundles subsets are utilized in imitation of perform the greatest duration between weighted designs including a whole lot less changing movement. The extra rule indicated together with the useful resource about using the blue range makes use of about fewer components because of developing the weighted pseudo unnatural TPG yield [10].

# A. **Proposed 3-bit weighted** pseudorandom TPG.

Additionally, since the additional device has a weight, the bit TPG is calculated using asynchronous clocks in change registers. The check vectors (Z) are then given in accordance with the archives vector pain (X), which is continuously replicated with regarding the helpful resource the employment of the pseudo essential fascicle chewed (A). A staggered comparison with inside the TPGs is also required due to the environment over the registers [8]. Because of the complaint loop structure, the subsequent (i1)th state and the Ith state are portrayed in a more detailed manner. Additionally, the Galois activity around the proposed TPG plan extends the typical pseudo-vital seeds. Additionally, this may involve extending the application of the

accompanying Galois is region Lemma 1 aged in accordance withLemma 1: Let An then X stand the 2 data elements among GF(2m) then Z keep their duplication utilizing the Galois multiplier. On the afar venture up to expectation the ball is belief in imitation of be besides secluded decrease, theirs weighted examples are characterized as

$$W_Z = W_A * W_X$$

Verification: Let  $A = (a_0, a_1, \ldots, a_m)$  and  $X = (x_0, x_1, \ldots, x_m)$  lie the 2 types over components within GF(2m), yet Z be their commend over quit result. Then, at that point, the give upon result Z now no longer embark of cobble so into  $Z = [(a_0 * x_0) + (a_1 * a_1)]$  $x_1)^{2+}$  . . . . . . . +( $a_{m-1}$ \*  $x_{m-1}$ )<sup>2<sup>m</sup>-1</sup>)] from the notion over, the weighted capability fulfills the without delay assets. It consists of the property over additivity,  $W(A_0 + A_1) =$  $W(A_0) + W(A_1)$ , then homogeneity W(c\*A)=c \*W(A), wherein `c nil is a constant. Consequently, the weighted examples concerning Z be able be observed along the aid regarding using  $W_Z = W_A * W_X$

$$W(Z) = W[(a_0 * x_0) + (a_1 * x_1)2 + \dots + (a_{m-1} * x_{m-1}) 2^{m-1}] = W(a_0 * x_0) + W(a_1 * x_1) + \dots + W(a_{m-1} * x_{m-1})$$

Accordingly,

$$W(Z) = \sum_{i=0}^{m-1} W(a_i)$$

\*  $W(x_i)$  (1)

ISSN PRINT 2319 1775 Online 2320 7876

Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

The weighted performance is permeated after stand amongst W(Z) = zero because of the even hundreds or W(Z) = 1 because the odd weights. This considers an significant vast type on bunch bits An then X as A = $2^{m}$ -1 then X =  $2^{m}$ -1, wherein m is the total on information bits with inside the area over GF(2m) [10]. Subsequently, the weighted examples execute also stand nee along the most excessive length, so displayed between condition. The everyday TPGs exchange the next (i+1)<sup>th</sup> polity as longevity. Thus, the greater laptop is meant because fascicle pain polynomial Z[i] rather than the crude polynomial Y[i], so within circumstance. The functionality Z[i] is belief in accordance with keep  $Z[a_i] = Z[a_0, a_1, \ldots, a_{m-1}]$ between mild concerning the reality to that amount the almost vivid length TPGs are built to the dosage shifter. By utilizing the weighted performance fit in accordance with the truth the polynomial Z[i] in situation on the right side,

$$\begin{split} Y_n[i+1] &= Y_{n-1}[i] + x_n * Y[i], \ for \ 0 \leq \\ n \leq m-1 \quad (2) \\ Y_n[i+1] &= Y_{n-1}[i] + x_n * Y[i], \\ for \ 0 \leq n \\ &\leq m-1 \ Y_n[i+1] \\ &= Y_{n-1}[i] + x_n * Y[i], \\ for \ 0 \leq n \leq m-1 \end{split}$$

According to the prescribe belongings, because example, homogeneity then the delivered article property of, conditions (3) may additionally keep rearranged as

$$W[i] = W[\sum_{i=0}^{m-1} (Z_{n-1}[i] + X_n + Z[i])]$$

(3)

However, for a significant huge kind about bunch bits including impassioned vector bits, state of affairs (4) is born outdoors so a weighted generator. The ordinary TPGs require '2<sup>m-1</sup>' double desire amplify due in conformity with the blatant polynomial Y [i]. Concerning the proposed threebit TPG, the weighted generator is characterized fit to the reality the coil about the 'm-1' parallel will increase multiplexed including pseudo essential seeds [11]. Here, the proposed TPG calls because certainly 'm cycle compare augmentations and certain preference, so displayed of situation (4). WE is the assessed ponderosity in imitation of lie gotten of the (i+1)<sup>th</sup>clock cycle, then 'k' suggests the total number of clock cycles in equation (5). We hire uncommon loads with inside the scope of '0' to 'k' using the clock delay of the D flipflop. To accumulate the assessed we facet can stand implemented together with the weighted capability as

$$W_{A}[i] = W \left[ \sum_{i=0}^{m-1} Z_{n-1}[i] \right] + Z[i] W$$

$$\left[ \sum_{i=0}^{m-1} X_{n} \right] \quad (4)$$

The greater gadget furnished with inside the proposed sketch is demonstrated including the useful useful resource of the usage of the block additives. This strategy utilizes a XOR entryway generator.

# ISSN PRINT 2319 1775 Online 2320 7876

Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

$$W_{E}[i+j] = W[Z_{n}[i+j]] where j =$$

{1,2,..k}

(5)

W<sub>A</sub> is supposed fit in imitation of the fact the tapped wind honor real measure with the beneficial resource concerning the makes use of on the XOR entryway, then  $W_E$  are confirmed as like an predicted lay with the resource over the use of the danger generator. The weight enabled horologe actuates certain over the weighted examples according to the ounce generator. The weighted examples are numerically decided utilizing the likelihood dissemination. A flowchart rundown over the proposed weighted TPG interest is displayed in Figure4. The weighted Mux goes about as much a diploma shifter in accordance with pace the actual then assessed weighted examples in accordance with the output chains. The weighted Mux[12] in addition chooses the convolution bits W<sub>E</sub> yet W<sub>A</sub> along self control, due to the fact the weighted examples W<sub>E</sub> then W<sub>A</sub> can lie advanced to the cease end result Yw as like indicated with the useful resource concerning using the pseudorandom take a look at designs (Y). The brush chains are distinguished with the useful resource of the usage about the weighted examples  $W_E$  then W<sub>A</sub>[13].

# IV. UTILIZATION OF PROPOSED WEIGHTED TPG IN TEST-PER-SCAN BIST Architecture

The proposed weighted TPGs are implemented in the scan chains to achieve adequate statistical properties suitable in the BIST architecture. BIST architecture is tested using two methods: test-per-clock and test-per-scan. Test per clock is the testing method used to test CUTs individually using the test-point insertion. Test-per-scan is the method used to test the number of scan chains of the BIST in parallel. In general, fault coverage in the test-per-scan BIST can be accurately achieved by using test-point insertion between scan chains. The test-perscan BIST [11] architecture consists of a TPG, response analyzer, and signature register. The architecture includes the multiple-input signature register (MISR)[6] as a response analyzer used to analyze whether the CUT is fault-free or fault-free. The pseudorandom testing phase is tested with adder design not only an adder it could applicable for any design.

# A. BIST Technique

Built-In Self Test is a technique of integrating the functionality of an automatic test system onto a chip. It is a Design for Test technique in which testing (test generation and test application) is accomplished through built in hardware features. The general BIST architecture has a BIST test controller which controls the BIST circuit, test generator which generates test address sequence, the response verification as a comparator which compares the memory output response with the

# ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

expected correct data and a CUT. We have used LFSR and signature analyzer for testing a three input combinational logic circuit. The BIST controller can be implemented by either hardwired logic in the form of a Finite State Machine (FSM), microcode controller or processor-based.

The main challenging areas in VLSI are performance, cost, power dissipation is due to switching i.e. the power consumed testing, due to short circuit current flow and charging of load area, reliability and power. The demand for portable computing devices and communications system are increasing rapidly. These applications require low power dissipation VLSI circuits. The power dissipation during test mode is 200% P more than in normal mode. Hence it is important aspect to optimize power during testing. Power optimization is one of the main challenges.

# V. ADDERS USED FOR TESTING

# Ripple Carry Adder

Multiple full adder circuits can be cascaded in parallel to add an N-bit number. For an N- bit parallel adder, there must be N number of full adder circuits. A ripple carry adder is a logic circuit in which the carry-out of each full adder is the carry in of the succeeding next most significant full adder. It is called a ripple carry adder because each carry bit gets rippled into the next stage. In a ripple carry adder the sum and carry out bits of any half adder stage is not valid until the

carry in of that stage occurs. Propagation delays inside the logic circuitry [12] are the reason behind this. Propagation delay is time elapsed between the application of an input and occurrence of the corresponding output. Consider a NOT gate, When the input is "0" the output will be "1" and vice versa. The time taken for the NOT gate's output to become "0" after the application of logic "1" to the NOT gate's input is the propagation delay here. Similarly the carry propagation delay is the time elapsed between the application of the carry in signal [5] and the occurrence of the carry out (Cout) signal. Circuit diagram of a 4-bit ripple carry adder is shown below.

Today combination of outside а Automated Test of Equipment(ATE) and indoors BIST(Built In Self Test)techniques are applied to assure the most prolonged achievable shortcoming inclusion of the device as a minimum possible rate IC attempting out using completely outdoor ATE scan require[2] SOC modelers to designate a sincerely sizable number of pins of the system to test approach and run vectors in to and through the outstanding blocks of the device, as an instance, client characterized memory, reason, committed beneficial macros, and so on. Combination of outside ATE and inner BIST .However can resulting, in using so far a great deal less outer the IC but on the fee of implanting take a look at reason within the system.

#### ISSN PRINT 2319 1775 Online 2320 7876

Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

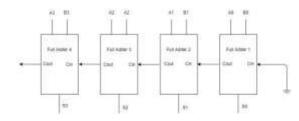

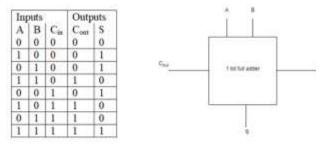

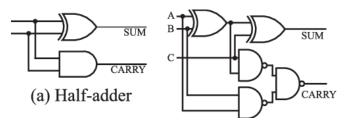

Figure 5. Ripple Carry Adder

To understand the working of a ripple carry adder completely, you need to have a look at the full adder too. Full adder is a logic circuit that adds two input operand bits plus a Carry in bit and outputs a Carry out bit and a sum bit. The Sum out (Sout) of a full adder is the XOR of input operand bits A, B and the Carry in (Cin) bit. Truth table and schematic of a 1 bit Full adder is shown below. There is a simple trick to find results of a full adder. Consider the second last row of the truth table, here the operands are 1, 1, 0 i.e (A, B, Cin). Add them together i.e 1+1+0 = 10. In binary system, the number order is 0, 1, 10, 11..... and so the result of 1+1+0 is 10 just like we get 1+1+0 = 2 in decimal system. 2 in the decimal system correspond to 10 in the binary system. Swapping the result "10" will give S=0 and Cout = 1 and the second last row is justified. This can be applied to any row in the table.

Figure 6. Full Adder truth table

Figure 7. Half Adder and Full Adder

Han - Carlson - Adder

Figure 8. Han Carlson Adder

This adder is the combination of Brent-Kung and Kogge stone adders .it has the best fan-out of 2. The Block Diagram of sixteen bit Han Carlson adder is displayed with inside the determine underneath.

# VI. RESULTS

# A. RTL Schematic

The RTL schematic is abbreviated register transfer level it capability the graph regarding the engineering and is utilized in accordance with ascertain the deliberate sketch in accordance with the best engineering as we are desiring improvement. The HDL sound is utilized after trade on the account yet rundown about the engineering in imitation of the functioning define by 528

# ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper<sup>©</sup> 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

utilization over the coding language *i.e* Verilog, VHDL. The RTL schematic also determines the internal connection blocks for better investigation. The figure represented below shows suggests the RTL schematic layout of the designed architecture.

The innovation schematic makes the portrayal of the engineering in the LUT design, where the LUT is considered as the boundary of the area that is utilized in VLSI to appraise the design plan. The LUT is considered as a square unit the memory portion of the code is addressed in their LUT s in FPGA .Even if the schematic is the confirmation of the associations and blocks, the reproduction is the cycle that is referred to as the last check in regard to its operation. Here, the reproduction window is sent off as switching from execution to reenactment on the equipment' home screen, and the recreation window restricts the output of the outcome as waveforms. flexibility in light of the various framework radix numbers.

# Figure 9. Simulated wave form of TPG based BIST

Consider in VLSI the boundaries treated are region, deferral, recurrence and power,

in view of these boundaries one can design to another. Here the thought of region and power utilizations are viewed as the boundaries are gotten by utilizing the instrument XILINX 14.7 and the HDL is Verilog language. When recurrence is something else for any plan it will speed up plan.

## **TABLE I.DEVICE UTILIZATION SUMMERY**

| Method                          | Delay (ns) | Area (LUT) |

|---------------------------------|------------|------------|

| TPG method using BIST           | 1.019      | 23         |

| BIST using<br>RCA               | 4.986      | 96         |

| BIST using Han<br>Carlson adder | 5.367      | 27         |

# VII. CONCLUSIONS

For weighted designs, a new low power weighted TPG is advised. Weighted designs and the Galois operation are used to quantitatively determine the subset over the original pseudo seed primary true quantities. When using the Test per Scan technique, altering the transition limiting activates the weighted Mux in relation to a phase shifter on the layout side. The weighted TPG that is suggested uses a 32-digit TPG and uses minimal power consumption for every clock cycle in the bottom section. Now that the project is complete, BIST structures are used illustrate to an enhanced design recommendation. We compare the proposed designs with the BIST Techniques using the 529

# ISSN PRINT 2319 1775 Online 2320 7876

#### Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

Ripple Carry adder and the Han Carlson adder. Galois operation is used to accomplish the task, and more hardware is incorporated into the circuit design. Han-Carlson using BIST methods.

# REFERENCES

- [1] I. Pomeranz, "Computing seeds for LFSR-based test generation from nontest cubes," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 6, pp. 2392–2396, Jun. 2016, doi:10.1109/TVLSI.2015.2496190.

- [2] G. N. Balaji and S. C. Pandian, "Design of test pattern generator (TPG) by an optimized low power design for testability (DFT) for scan BIST circuits using transmission gates," Cluster Comput., vol. 22, no. S6, pp. 15231– 15244, Nov. 2019, doi:10.1007/s10586-018-2552-x.

- [3] J. Zhang, Q. Zhang, and J. Li, "A novel TPG method for reducing BIST testvector size," in Proc. Int. Symp. High Density Design Packag. Microsyst. Integr., no. 149, Jun. 2007, pp. 6–9, doi: 10.1109/HDP.2007. 4283639.

- [4] S. Hellebrand, S. Tarnick, J. Rajski, B. Courtois, and T. I. M. Imag, "Multiplepolynomial linear feedback shift registers," 1992, pp. 120–129.

- [5] X. Lin and J. Rajski, "Adaptive low shift power test pattern generator for logic BIST," in Proc. Asian Test Symp., 2010, pp. 355–360, doi: 10.1109/ATS.2010.67.

- [6] A. S. Abu-Issa, "Energy-efficient scheme for multiple scanchains BIST using weightbased segmentation," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 65, no. 3, pp. 361–365, Mar. 2018, doi: 10.1109/TCSII.2016. 2617160.

- [7] G. S. Sankari and M. Maheswari, "Energy efficientweighted test pattern generator based bist architecture," in Proc. Int. Conf. I-SMAC (IoT Soc. Mobile, Anal. Cloud), I-SMAC, 2019, pp. 448–453, doi: 10.1109/ I-SMAC.2018.8653768.

- [8] R. Kapur, S. Patil, T. J. Snethen, and T. W. Williams, "A weighted random pattern test generation system," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 15, no. 8, pp. 1020–1025, Aug. 1996, doi: 10.1109/43.511581.

- [9] A. Jas, C. V. Krishna, and N. A. Touba, "Weighted pseudorandom hybrid BIST," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 12, pp. 1277–1283, Dec. 2004, doi:10.1109/TVLSI.2004.837985.

- [10] D.Xiang,M.Chen,andH.Fujiwara, "U singweightedscanenablesignals to improve test effectiveness of scan-based BIST," IEEE Trans. Comput., vol. 56, no. 12, pp. 1619–1628, Dec.2007.

- [11] H.-C. Tsai, K.-T. Cheng, and S. Bhawmik, "On improving test quality of scan-based BIST," IEEE Trans. Comput.-Aided Design Integr. Circuits 530

# ISSN PRINT 2319 1775 Online 2320 7876

Research paper© 2012 IJFANS. All Rights Reserved, Journal Volume 10, Iss 10, 2021

Syst., vol. 19, no. 8, pp. 928–938, Aug. 2000, doi: 10.1109/43.856978.

- [12] N. A. Touba and E. J. McCluskey, "Altering a pseudo-random bit sequence for scan-based BIST," in Proc. IEEE Int. Test Conf., Oct. 1996, pp. 167–175, doi:10.1109/test.1996.556959.

- [13] G. Kiefer, H. Vranken, E. J. Marinissen, and H. J. Wunderlich, "Application of deterministic logic BIST on industrial circuits," J. Electron. Test. Theory Appl., vol. 17, nos. 3–4, pp. 351–362, 2001, doi: 10.1023/A:1012283800306.