# © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -1) Journal Volume 8, Issue 3, 2019 Design of a Low-Power Linearized Subthreshold Operational Transconductance Amplifier (OTA) using Multiple Input Floating-Gate (MIFG) Optimizing

# M. Lakshmana Kumar<sup>1</sup>

<sup>1</sup> Department of ECE, Koneru Lakshmaiah Education Foundation

## Abstract:

The paper proposes an new approach of enhancing the linearity of metal-insulatorferroelectric-gate (MIFG) MOS transistor-based subthreshold operational transconductance amplifiers (OTAs). Using the ferroelectric gate material, one of the distinctive features of MIFG MOS transistors, this method improves OTA performance without compromising energy efficiency. Through theoretical modeling and simulation investigations, the proposed linearized subthreshold OTA architecture is investigated. Nonlinearity compensation techniques have been developed, enhancing linearity in the subthreshold area over a wide range of input signal amplitudes. In addition, the investigation examines into design elements influence overall linearity and power consumption. Enticing applications for such linearized subthreshold OTA encompass sensor interfaces, battery-operated devices, and ultra-lowpower analog signal processing.

**Keywords:** Operational Transconductance Amplifier (OTA), Metal-Insulator-Ferroelectric-Gate (MIFG) MOS Transistors, Low power, Linearity Enhancement.

# 1. Introduction

Energy-efficient integrated circuit development is becoming more and more important in the context of contemporary electronic systems, especially for battery-operated gadgets and Internet of Things (IoT) applications. Operational transconductance amplifiers (OTAs) in the subthreshold range present an effective choice for addressing the demanding power requirements of such types of applications. However, obtaining reliability in analog signal processing is severely hindered by the subthreshold operation's intrinsic nonlinearity.

*Research paper* © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019 The article discusses this difficulty by presenting a novel method of integrating Metal-Insulator-Ferroelectric-Gate (MIFG) MOS transistors to improve the linearity of subthreshold OTAs. As a result of their ultra-low power consumption and subthreshold functioning, OTAs are a great choice for situations where energy saving is crucial. Low power has advantages, but linearity—a critical aspect of analog circuits that directly impacts signal processing fidelity—is sacrificed in the process. [1]-[6].

MIFG MOS transistors have been incorporated into subthreshold OTAs, which is a deviation from traditional design techniques. Because of its special ferroelectric gate material, MIFG MOS transistors present a modified approach to solving the nonlinearity issues associated with subthreshold operation. The transistor has memory effects and hysteresis due to the ferroelectric property of the gate material, which can be used to counteract the nonlinear behavior seen in conventional subthreshold OTAs. Through the unique properties of MIFG MOS transistors and the benefits of subthreshold operation, this research intends to broaden up fresh prospects for OTA design that simultaneously balance linearity and energy efficiency.

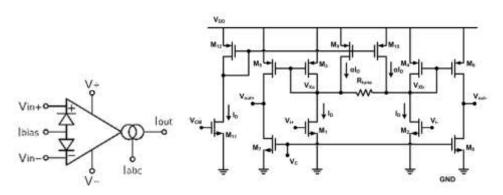

Fig1: Operational Transconductance Amplifier (OTA)[1]

## 2. Design Methodology:

The design process begins with the careful selection of Metal-Insulator-Ferroelectric-Gate (MIFG) MOS transistors. The MIFG MOS transistors chosen for integration into the subthreshold OTA are characterized by their ferroelectric gate material[4]-[7]. This selection is crucial as it introduces unique hysteresis and memory effects that will be exploited for compensating nonlinearity in the subthreshold region. The overall architecture of the linearized subthreshold OTA is based on a traditional subthreshold OTA design, augmented by the inclusion of MIFG MOS transistors in key positions. The ferroelectric gate material

*Research paper* © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -1) Journal Volume 8, Issue 3, 2019 introduces a controllable memory effect that plays a pivotal role in shaping the linearity characteristics of the amplifier.

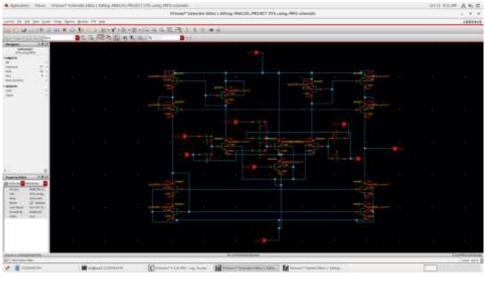

Fig2: Simulation Circuit of OTA

# 2.1 Linearization Technique

The linearization technique relies on the exploitation of the ferroelectric properties of the MIFG MOS transistors. During operation, the hysteresis and memory effects in the ferroelectric gate material are leveraged to dynamically adjust the transistor characteristics, compensating for the nonlinearity inherent in subthreshold OTAs[8]. This adaptive compensation mechanism aims to counteract the variations in transistor behavior and enhance linearity over a broad range of input signal amplitudes.

## 3. Results

The overall performance of the linearized subthreshold OTA is evaluated based on various criteria, including linearity, power efficiency, and noise characteristics. Comparative analyses are conducted with traditional subthreshold OTAs to highlight the advantages gained through the integration of MIFG MOS transistors. Key design parameters[10], such as transistor dimensions, biasing conditions, and feedback configurations, are systematically optimized to achieve the desired trade-off between linearity and energy efficiency. This step involves an iterative process of simulation and parameter adjustment to fine-tune the performance of the linearized subthreshold OTA.

|  |  |        | $\Box O \Box C$ |

|--|--|--------|-----------------|

|  |  | Online | /8/6            |

|  |  |        |                 |

© 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019

| Devices            | W/L (µm) | I <sub>D</sub> (nA) | Inversion coefficient |

|--------------------|----------|---------------------|-----------------------|

| M <sub>1,2</sub>   | 200/15   | 0.5 - 200           | 0.006 - 0.07          |

| M <sub>3</sub>     | 160/3    | 2-400               | 0.006 - 0.07          |

| M4-M7              | 3.4/488  | 0.5 - 200           | 0.3 - 148             |

| M8, M9             | 3.4/180  | 0.5 - 200           | 0.4 - 158             |

| M <sub>0</sub>     | 350/60   | 4 - 800             | 0.016 - 0.34          |

| M <sub>caseN</sub> | 4/190    | 0.5 - 200           | 0.2 - 1.36            |

| McascP             | 4/100    | 0.5 - 200           | 0.23 - 2.87           |

#### Table 1: OTA Transistors Dimension

#### 4. Conclusion

This comprehensive design and methods approach ensures a systematic exploration of the proposed linearized subthreshold OTA, from the selection of MIFG MOS transistors to the final validation of the fabricated circuit's performance. The integration of theoretical modeling, simulation studies, and practical measurements contributes to a thorough understanding and optimization of the linearization technique. The low-voltage, subthreshold Operational Transconductance Amplifier (OTA) suitable for low-frequency applications has been introduced. Through the utilization of Metal-Insulator-Ferroelectric-Gate (MIFG) MOS devices and the incorporation of a cubic-distortion-term-cancelling technique, the OTA has demonstrated an expansive linear range of 1.1 Vpp under a 1.5-V power supply, as confirmed by testing results. Addressing secondary effects such as parasitic capacitances, parameter errors, mismatches, and charge entrapment, the offset error of the OTA can be mitigated by adjusting the biasing voltages of the input MIFG MOS transistors.

#### References

F. Rezaei and S. J. Azhari, "A Highly Linear Operational Transconductance Amplifier (OTA) with High Common Mode Rejection Ratio," 2010 International Conference on Signal Acquisition and Processing, Bangalore, India, 2010, pp. 18-22, doi: 10.1109/ICSAP.2010.39.

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019

- V. Saravanan, R. Anu Priya and B. Venkatalakshmi, "Design of Optimal Amplifier for Wearable Devices," 2011 International Conference on Process Automation, Control and Computing, 2011, pp. 1-4, doi: 10.1109/PACC.2011.5978981

- S. S. Rajput and S. S. Jamuar, "Low voltage analog circuit design techniques," in IEEE Circuits and Systems Magazine, vol. 2, no. 1, pp. 24-42, 2002, doi: 10.1109/MCAS.2002.999703. https://ptm.asu.edu/

- S. -W. Pan, C. -C. Chuang, C. -H. Yang and Y. -S. Lai, "A novel OTA with dual bulk-driven input stage," 2009 IEEE International Symposium on Circuits and Systems, 2009, pp. 2721- 2724, doi: 10.1109/ISCAS.2009.5118364.

- H. S. Raghav, B. P. Singh and S. Maheshwari, "Design of low voltage OTA for biomedical application," 2013 Annual International Conference on Emerging Research Areas and 2013 International Conference on Microelectronics, Communications and Renewable Energy, 2013, pp. 1-5, doi: 10.1109/AICERA-ICMiCR.2013.6576034.

- H. S. Raghav, B. P. Singh and S. Maheshwari, "Design of low voltage OTA for biomedical application," 2013 Annual International Conference on Emerging Research Areas and 2013 International Conference on Microelectronics, Communications and Renewable Energy, 2013, pp. 1-5, doi: 10.1109/AICERA-ICMiCR.2013.6576034/

- H. Khameh and H. Shamsi, "A sub-1V high-gain two-stage OTA using bulk-driven and positive feedback techniques," Proceedings of Papers 5th European Conference on Circuits and Systems for Communications (ECCSC'10), 2010, pp. 103-106.

- E. Cabrera-Bernal, S. Pennisi and A. D. Grasso, "0.7-V bulk-driven three-stage class-AB OTA," 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), 2015, pp. 1-4, doi: 10.1109/NEWCAS.2015.7182069

- 9. Behzad Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill Education Limited, 2018.

- L. H. C. Ferreira and S. R. Sonkusale, "A 60-dB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 6, pp. 1609-1617, June 2014, doi: 10.1109/TCSI.2013.2289413.

- 11. M. F. Mauludin, D. -H. Lee and J. Kim, "Wideband Operational Trans-Conductance Amplifier with Feed-Forward Compensation Technique," 2001 18th International

- Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -1) Journal Volume 8, Issue 3, 2019 SoC Design Conference (ISOCC), 2001, pp. 298-299, doi: 10.1109/ISOCC53507.2021.9613868.

- A. E. Mourabit, Guo-Neng Lu and P. Pittet, "Wide-linear-range subthreshold OTA for low-power, low-Voltage, and low-frequency applications," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52, no. 8, pp. 1481-1488, Aug. 2005, doi: 10.1109/TCSI.2005.852011.

- L. Watts, D. A. Kerns, R. F. Lyon and C. A. Mead, "Improved implementation of the silicon cochlea," in IEEE Journal of Solid-State Circuits, vol. 27, no. 5, pp. 692-700, May 1992, doi: 10.1109/4.133156

- 14. A. Veeravalli, E. Sanchez-Sinencio and J. Silva-Martinez, "Transconductance amplifier structures with very small transconductances: a comparative design approach," in IEEE Journal of Solid-State Circuits, vol. 37, no. 6, pp. 770-775, June 2002, doi: 10.1109/JSSC.2002.1004582.